Der Watchdog-Timer (WDT) ist eines der wichtigsten Sicherheitsnetze, wenn Sie industrielle PIC-Steuerungen gegen Software-Hänger, EMV-bedingte Störungen und seltene Randzustände absichern möchten. In rauen Umgebungen laufen Mikrocontroller oft jahrelang ohne Neustart: in Schaltschränken mit Frequenzumrichtern, an langen Sensorleitungen, bei Temperaturschwankungen oder unter sporadischen Spannungseinbrüchen. Genau dort zeigen sich Fehlerbilder, die im Labor kaum auftreten: Ein Interrupt bleibt aus, eine Kommunikationsroutine wartet endlos auf ein Flag, ein Stack läuft über, ein Speicherbit kippt durch Störeinfluss oder ein Peripheriemodul hängt in einem undefinierten Zustand. Der WDT wirkt hier wie ein unabhängiger „Aufpasser“: Er erwartet, dass Ihre Firmware in regelmäßigen Abständen ein definiertes Lebenszeichen sendet. Bleibt dieses Lebenszeichen aus, setzt der Watchdog das System kontrolliert zurück oder löst – je nach PIC-Familie und Konfiguration – einen definierten Recovery-Pfad aus. Damit ist der WDT kein „Nice-to-have“, sondern ein zentraler Baustein für Verfügbarkeit, Wartbarkeit und Betriebssicherheit. Entscheidend ist jedoch die richtige Umsetzung: Ein falsch eingesetzter Watchdog kann Probleme verdecken, unnötige Resets erzeugen oder Sicherheitsfunktionen unterlaufen. In diesem Artikel erfahren Sie, wie Sie den Watchdog-Timer bei PIC-Mikrocontrollern praxisnah konfigurieren und so einsetzen, dass industrielle Steuerungen nach Störungen sauber in einen sicheren Zustand zurückfinden.

Was ein Watchdog-Timer leistet und was nicht

Ein WDT ist ein Hardware-Timer, der unabhängig von Ihrer normalen Programmlogik läuft. Wenn die Firmware den Timer rechtzeitig „füttert“ (häufig als „Clear/Service/Kick“ bezeichnet), bleibt das System aktiv. Wenn nicht, löst der Watchdog einen Reset oder ein definiertes Ereignis aus. Damit adressiert der WDT primär diese Risiken:

- Software-Deadlocks: Endlosschleifen, blockierende Wartebedingungen, verlorene Interrupts.

- Temporäre Peripheriefehler: Hängende Kommunikationsmodule, Timing-Glitches, Zustandsautomaten, die nicht weiterlaufen.

- Störungen von außen: EMV/ESD-Effekte, die Register oder Speicher beeinflussen können.

- Unbeabsichtigte Laufzeitfehler: Stack-Überläufe, Speicherfragmentierung, seltene Race Conditions.

Nicht leisten kann der WDT allein: funktionale Sicherheit im Sinne einer vollständigen Gefahrenbeherrschung. Er ist ein Recovery-Mechanismus, kein Ersatz für sichere Hardwarearchitektur, redundante Abschaltungen oder geprüfte Sicherheitskonzepte. In der Praxis ist der WDT ein Baustein in einer Kette aus Brown-out-Reset, plausiblen Default-Zuständen, sicherem Ausgangsdesign und klarer Fehlerbehandlung.

Warum der WDT in industriellen PIC-Steuerungen besonders wichtig ist

Industrielle Anlagen verlangen Verfügbarkeit und deterministisches Verhalten. Ein sporadischer Hänger kann bereits ausreichen, um Stillstand, Ausschuss oder Folgeschäden zu verursachen. Der WDT ist deshalb in vielen Branchen Standard, weil er zwei Dinge verbessert:

- Ausfallzeit minimieren: Statt dauerhaft zu hängen, startet das System automatisch neu.

- Fehler beherrschbar machen: Resets werden gezielt detektiert, protokolliert und führen zu definierten Startzuständen.

Gerade in EMV-kritischen Umgebungen wirkt der Watchdog wie eine „Selbstheilung“ für seltene Störereignisse. Wichtig ist dabei: Der Reset darf nicht zu unsicheren Ausgängen führen. Deshalb müssen Sie Ausgänge (Relais, PWM, Ventile, Motoren) so designen, dass sie bei Reset in einen sicheren Zustand gehen oder hardwareseitig verriegelt werden.

Grundprinzip: Timeout richtig wählen und nachvollziehbar berechnen

Die Auswahl des WDT-Timeouts ist eine Kernentscheidung. Er muss lang genug sein, damit legitime Verarbeitung (z. B. Kommunikations-Timeouts, Flash-Schreibzyklen, Sensorabfragen) nicht unnötig zu Resets führt, aber kurz genug, um echte Hänger schnell zu beheben. Eine einfache Planungsgröße ist die maximale erwartete „Lebenszeichen-Latenz“ Ihrer Firmware.

Timeout als Verhältnis von Worst-Case-Laufzeit und Sicherheitsfaktor

Eine praktikable Heuristik ist:

Dabei ist

WDT-Varianten: Standard-, Windowed- und Low-Power-Watchdog

Je nach PIC-Familie kann der Watchdog mehr können als nur „Reset nach Timeout“.

- Standard-WDT: Reset, wenn das Service nicht rechtzeitig erfolgt.

- Windowed Watchdog: Service ist nur in einem Zeitfenster erlaubt; zu frühes oder zu spätes Füttern gilt als Fehler. Das verhindert, dass eine „defekte“ Schleife den WDT ständig zu früh zurücksetzt.

- Low-Power- und Sleep-Szenarien: Manche Controller bieten Optionen, ob der WDT im Sleep weiterläuft oder separat konfiguriert wird.

Für industrielle Steuerungen ist der windowed Ansatz besonders interessant, wenn Sie verhindern möchten, dass ein unkontrollierter Codepfad den Watchdog „zufällig“ bedient, obwohl die Logik längst nicht mehr korrekt arbeitet.

Konfiguration bei PIC: Fuses, Register und typische Stolperfallen

Bei PIC-Mikrocontrollern wird die Watchdog-Nutzung oft über Konfigurationsbits (Fuses) sowie Laufzeitregister gesteuert. Typische Optionen sind: WDT grundsätzlich ein/aus, Prescaler/Divider für Timeout, Verhalten in Sleep/Idle, sowie Reset-Ursachen-Flags. Da sich Namen und Details je nach Familie unterscheiden, ist die wichtigste Regel: Arbeiten Sie konsequent nach Datenblatt und Errata Ihres konkreten Bausteins. Einstiegspunkte sind die offiziellen Microchip-Ressourcen, etwa über die Microchip Dokumentensuche sowie die Entwicklungsumgebung MPLAB X IDE.

Stolperfalle „WDT aus Versehen deaktiviert“

In vielen Teams passiert es mindestens einmal: Im Debug-Build wird der WDT deaktiviert, im Release-Build vergessen zu aktivieren oder umgekehrt. Abhilfe schaffen klare Build-Profile und ein Start-up-Selbsttest, der prüft, ob die erwartete WDT-Konfiguration aktiv ist und dies in einem Diagnose-Register/Log ablegt.

WDT richtig „füttern“: Kein Alibi-Kick, sondern ein Lebenszeichen aus Logik

Der häufigste Fehler ist ein Watchdog-Kick an der falschen Stelle, etwa in einer sehr schnellen Hauptschleife oder in einem Timer-Interrupt, der auch dann weiterläuft, wenn die eigentliche Applikation bereits hängt. Dann verliert der WDT seine Schutzwirkung. Gute Praxis: Der Watchdog darf nur dann zurückgesetzt werden, wenn zentrale Systemkriterien erfüllt sind.

- Heartbeat aus Zustandsautomat: Der WDT wird nur bedient, wenn der Hauptzustandsautomat einen „gesunden“ Zyklus abgeschlossen hat.

- Mehrere „Alive“-Bedingungen: Kommunikationsstack lebt, Sensorik plausibel, Ausgänge in gültigem Zustand, keine Fehlerflags.

- Kein WDT-Kick in ISR als Standard: Interrupts können weiterlaufen, während die Applikation hängt. ISR-Kicks sind nur in gut begründeten Sonderfällen sinnvoll.

Watchdog-Gating als robustes Muster

Ein bewährtes Muster ist „Gating“: Mehrere Module setzen jeweils ein Flag „OK“. Nur wenn alle Flags innerhalb eines definierten Zyklus gesetzt wurden, wird der Watchdog bedient. So koppeln Sie den WDT an echte Systemgesundheit statt an reine Taktaktivität.

WDT und Kommunikationsprotokolle: Timeouts sauber integrieren

Kommunikationsfehler sind typische Hänger-Auslöser: Ein Treiber wartet auf ein Byte, ein Bus bleibt blockiert, ein Slave zieht die Leitung. Statt den Watchdog als „Notbremse“ für jede Störung zu missbrauchen, sollten Kommunikationsschichten eigene Timeouts besitzen. Der WDT ist dann die letzte Instanz, wenn trotz Timeouts keine Rückkehr in einen definierten Zustand gelingt.

- UART: Receive-Timeout, Frame-Timeout, klare Reset-Strategie für Peripherie.

- I2C: Bus-Recovery (SCL toggeln, Modul resetten), Timeout für Transaktionen.

- SPI: Timeout bei Busy-Waits, saubere CS-Logik, Reset bei „stuck“ Zuständen.

- RS485/CAN: Fehlerzähler und Re-Init-Mechanismen, bevor WDT greift.

Erst wenn diese lokalen Recovery-Mechanismen scheitern, sollte der Watchdog den kompletten Reset auslösen. So bleibt das System stabiler und vermeidet unnötige Neustarts.

WDT und Sleep/Low Power: Industrial heißt nicht immer „dauerhaft voll aktiv“

Auch in der Industrie gibt es energieoptimierte Geräte: batteriebetriebene Sensoren, Funkknoten oder Wake-on-Event-Systeme. Hier muss der WDT bewusst geplant werden: Läuft er im Sleep weiter, muss die Firmware rechtzeitig aufwachen oder den Timeout anpassen. Wird der WDT im Sleep deaktiviert, brauchen Sie alternative Sicherheitsmechanismen (z. B. externe Watchdogs oder Wakeup-Strategien), wenn ein „Hängen im Sleep“ relevant ist.

Externer Watchdog vs. interner WDT: Wann sich zusätzliche Hardware lohnt

Der interne WDT ist oft ausreichend, aber nicht in allen Fällen. Ein externer Watchdog-IC kann Vorteile bringen, insbesondere wenn Sie auch Fehler in der internen Clock-Domäne, Versorgungseinbrüche oder MCU-interne Blockaden absichern müssen.

- Vorteile externer Watchdogs: Unabhängig vom Mikrocontroller, oft bessere Diagnoseausgänge, kann auch Versorgung überwachen.

- Nachteile: Mehr Bauteile, Layoutaufwand, potenziell neue Fehlerquellen, Kosten.

In sicherheitskritischen oder sehr EMV-belasteten Systemen wird häufig eine Kombination genutzt: interner WDT für schnelle Software-Hänger und externer Watchdog als übergeordnete Instanz.

Reset-Ursache auswerten: WDT-Reset ist ein Diagnoseereignis

Ein Watchdog-Reset sollte nicht „still“ passieren. In industriellen Systemen ist es wertvoll zu wissen, warum das Gerät neu gestartet hat. Viele PICs bieten Statusflags für Reset-Ursachen (z. B. Power-on, Brown-out, WDT, MCLR). Gute Praxis ist:

- Reset-Cause früh auslesen: direkt zu Beginn des Start-up, bevor Flags überschrieben werden.

- Persistentes Logging: Zähler im EEPROM/Flash oder in einem Backup-RAM-Bereich, um Häufigkeiten zu erkennen.

- Service-Interface: Diagnose über UART, CAN, Modbus oder Service-LED-Codes ausgeben.

Damit wird der WDT zum Werkzeug für Feldanalyse: Sie erkennen Muster (z. B. Resets nur bei Motorstart, nur bei hoher Temperatur) und können EMV- oder Timing-Probleme gezielt adressieren.

Sichere Startzustände: Nach dem Reset muss die Anlage kontrolliert bleiben

Ein Reset ist nur dann eine „gute“ Recovery, wenn das System danach sicher hochkommt. Das betrifft sowohl Hardware als auch Firmware:

- Ausgänge default-sicher: Pull-down/Pull-up so wählen, dass Relais und Treiber beim Reset nicht ungewollt schalten.

- Initialisierung in Phasen: Erst Versorgung stabilisieren und Peripherie in sicheren Modus, dann Kommunikation, dann Aktorik.

- Sanfter Wiederanlauf: Ramp-up von PWM, validierte Sensorwerte, Plausibilitätsprüfungen vor Freigabe.

In industriellen PIC-Steuerungen ist der Reset-Start oft als definierter Zustandsautomat umgesetzt: „SAFE → INIT → SELFTEST → RUN“. Der Watchdog passt ideal zu diesem Muster, weil er einen Sprung zurück nach SAFE erzwingt, wenn RUN nicht mehr zuverlässig erreicht wird.

Teststrategie: WDT absichern heißt WDT gezielt provozieren

Ein Watchdog, der nie getestet wird, ist im Feld eine Wette. Gute Teams planen bewusst Tests ein, die WDT-Resets auslösen und überprüfen, ob das System danach korrekt reagiert.

- Deadlock-Test: absichtlich eine Endlosschleife oder blockierenden Wait einbauen (per Testflag), um WDT-Reset zu validieren.

- Kommunikations-Hänger: Bus blockieren, Slave abziehen, Leitungen kurzzeitig stören und Recovery beobachten.

- EMV-nahe Tests: Brownout-Simulation, Lastsprünge, ESD-nahe Steckerevents (mit geeigneten Sicherheitsvorkehrungen).

- Reset-Cause-Verifikation: Prüfen, ob Diagnose korrekt „WDT-Reset“ erkennt und protokolliert.

Best Practices für robuste industrielle WDT-Implementierung

- WDT nur bei „Gesundheit“ bedienen: nicht in einer beliebigen Schleife, sondern nach validierten Zyklusbedingungen.

- Timeout datenbasiert wählen: Worst-Case messen (inkl. Kommunikation und Flash-Schreiben), dann Sicherheitsfaktor anwenden.

- Reset-Cause speichern: WDT-Reset zählen und für Service zugänglich machen.

- Startzustände absichern: Hardware-Pulls, Treiberfreigaben, sichere Defaults.

- Watchdog nicht als Fehlerkaschierer: Wenn WDT regelmäßig auslöst, ist das ein Qualitäts- oder EMV-Thema, das analysiert werden muss.

- Build-Disziplin: Debug/Release klar trennen, WDT-Konfiguration prüfen, reproduzierbare Toolchain nutzen.

Weiterführende Informationsquellen

- Microchip Dokumentensuche für Datenblätter, Errata und Referenzhandbücher: Microchip Dokumentensuche

- MPLAB X IDE als Standardumgebung für PIC-Entwicklung und Debugging: MPLAB X IDE

- MPLAB XC Compiler (C-Toolchain, je nach PIC-Familie): MPLAB XC Compilers

- Allgemeiner Überblick zum Watchdog-Prinzip: Watchdog (Überblick)

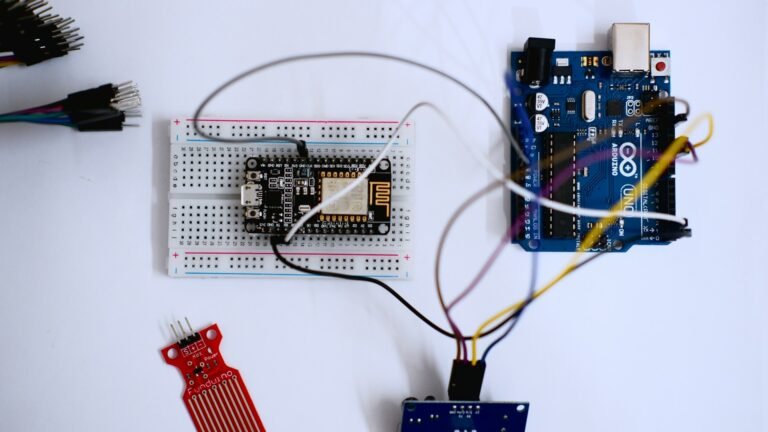

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.