Die I2S-Schnittstelle am PIC32 ist der Schlüssel, wenn Sie digitale Audio-Daten nicht nur „irgendwie“ übertragen, sondern auf einem Niveau verarbeiten möchten, das in Richtung professioneller Audiotechnik geht: saubere Taktführung, konstante Latenz, stabile Streams und ein Datenpfad, der auch bei 48 kHz oder 96 kHz nicht ins Stolpern gerät. I²S (Inter-IC Sound) ist dafür seit Jahren der Standard, um Audio-Codecs, DACs, ADCs oder digitale Audio-Module seriell anzubinden. Der große Vorteil gegenüber „Audio über SPI“ im klassischen Sinn: I²S definiert ein Audio-taugliches Timing (Word Select/LRCLK), eine klare Kanalzuordnung (links/rechts) und typische Wortbreiten (16/24/32 Bit), die zu Codecs passen. Gleichzeitig ist Audio gnadenlos ehrlich: Wenn die Clock-Quelle nicht sauber ist, Puffer überlaufen, DMA falsch eingestellt ist oder die Word-Select-Flanke nicht zum Datenfenster passt, hören Sie es sofort – als Knacksen, Dropouts, Verzerrung oder wandernde Kanäle. Dieser Beitrag zeigt Ihnen, wie Sie I²S auf PIC32-Systemen professionell angehen: von der Signallehre über Takt- und Datenraten, DMA/Pufferung, Treiberkonzepten in MPLAB Harmony bis hin zu typischen Fehlerbildern und deren Ursachen.

I²S in der Praxis: Signale, Rollen und typische Parameter

Ein klassischer I²S-Bus besteht aus wenigen Leitungen, die jedoch exakt zusammenspielen müssen. Üblich sind:

- BCLK (Bit Clock): Takt für die einzelnen Datenbits.

- LRCLK/WS (Word Select): Kanalumschaltung links/rechts (meist: Low = links, High = rechts).

- SD (Serial Data): die eigentlichen Audio-Daten (eine Leitung pro Richtung).

- MCLK (Master Clock, optional): Referenztakt für den Codec (z. B. 256 × Fs), je nach Baustein zwingend oder optional.

Je nach System übernimmt Ihr PIC32 die Rolle des Taktmasters (er erzeugt BCLK/LRCLK/MCLK) oder er läuft als Slave und lässt sich takten. Für stabile Audio-Setups ist ein klarer „Clock Master“ essenziell: Zwei Master auf einem Bus führen praktisch immer zu Timing-Konflikten.

Eine gut verständliche Referenz zur Grundidee des I²S-Busses bietet die I²S-Busspezifikation von NXP (Philips-Ursprung), die Timing und Grundstruktur erläutert: I2S Bus Specification (NXP, PDF).

PIC32 und I²S: Welche Hardware steckt dahinter?

Bei vielen PIC32-Familien ist I²S nicht als völlig separates Peripheriemodul ausgeführt, sondern als Audio-Protokollmodus innerhalb einer seriellen Schnittstelle (typischerweise SPI-ähnliche Hardware mit Audio-Mode). In Microchips PIC32-Referenzhandbuch wird dieser Ansatz im SPI-Kapitel beschrieben, inklusive Audio Protocol Interface Mode für I²S, Left/Right-Justified und PCM/DSP-Varianten: PIC32 FRM: SPI-Kapitel mit Audio Protocol Interface Mode (PDF).

Für die Firmware-Umsetzung in MPLAB Harmony ist außerdem wichtig: Harmony abstrahiert die unterschiedlichen I²S-fähigen Peripherien (z. B. SPI/I2S-Mode) über PLIBs und Treiber. Microchip beschreibt ausdrücklich, dass auf PIC32MX/MZ das I²S-Peripheral mit der SPI-Hardware geteilt ist: Harmony: SPI-I2S Peripheral Library Help.

Datenraten richtig planen: Sample Rate, Word Width und BCLK

Audio ist planbar, wenn Sie die Zusammenhänge sauber rechnen. Die zentrale Frage lautet: Wie schnell muss BCLK laufen, damit Ihre gewünschten Audio-Parameter übertragen werden können? Eine praxistaugliche Näherung lautet:

Dabei ist

Wenn Ihr Frame z. B. 2 Slots à 32 Bit nutzt, ergibt sich bei 48 kHz ein BCLK von 48.000 × 64 = 3,072 MHz. Das ist für PIC32 grundsätzlich gut beherrschbar, solange DMA/Pufferung stimmen und das Layout sauber ist.

MCLK: Wann Sie ihn wirklich brauchen

Viele Audio-Codecs erwarten einen Master-Clock (MCLK) als Vielfaches der Abtastrate, beispielsweise 256 × Fs oder 512 × Fs. Bei 48 kHz wären 256 × Fs = 12,288 MHz. Ob MCLK erforderlich ist, hängt vom Codec ab. Einige Bausteine können intern aus BCLK/LRCLK ableiten, andere benötigen MCLK zwingend, um ihre PLL sauber zu betreiben. Prüfen Sie das konsequent im Datenblatt Ihres Codecs, bevor Sie das PCB layouten.

Clocking auf Profi-Niveau: Jitter, PLL und Synchronität

Bei Audio wird Clockqualität hörbar. Jitter (zeitliches Zittern der Clockflanken) kann sich – je nach System – als Verzerrung oder „Unruhe“ bemerkbar machen, insbesondere bei hochwertigen DACs und empfindlichen Analogstufen. Für PIC32-Projekte bedeutet das:

- Konstante Clock-Quelle bevorzugen: saubere Quarze/Resonatoren, stabile PLL-Konfiguration.

- Ein Master im System: Entweder Codec oder PIC32 liefert die Referenz, nicht beide.

- Asynchrone Domänen vermeiden: Wenn USB-Audio, Bluetooth oder Netzwerk im Spiel sind, brauchen Sie klare Takt-Domänen und Pufferstrategien.

In vielen professionellen Designs wird die Audio-Clock vom Codec (oder von einem dedizierten Audio-Oszillator) bestimmt, während der Mikrocontroller sich anpasst. In PIC32-Projekten ist es jedoch häufig praktikabel, den PIC32 als Master zu verwenden – solange Sie die Grenzen kennen und nicht „nebenbei“ den Takt umkonfigurieren, während Audio läuft.

DMA und Pufferung: Der entscheidende Unterschied zwischen „geht“ und „klingt gut“

Audio-Streaming ist eine Dauerlast. Wenn die CPU jedes Sample einzeln schiebt, ist der Dropout vorprogrammiert – spätestens, wenn noch UI, Sensorik oder Kommunikation laufen. Deshalb ist DMA (Direct Memory Access) in PIC32-Audio-Projekten praktisch Pflicht. Das Ziel ist ein stabiler Datenfluss: I²S schiebt Daten, DMA füllt/leert Buffer, die CPU arbeitet blockweise.

- Double Buffering: Während Buffer A ausgegeben wird, füllt die CPU Buffer B nach (Ping-Pong).

- Ringbuffer: Für variable Latenzen (z. B. Netzwerk) wird ein größerer FIFO-Buffer genutzt.

- Interrupts nur pro Block: Interrupt pro Sample ist zu teuer; pro Block ist realistisch.

Blockgröße und Latenz sauber abwägen

Größere Blöcke reduzieren Interruptlast, erhöhen aber die Latenz. Kleinere Blöcke sind latenzarm, aber CPU-intensiver. Eine einfache Latenzabschätzung pro Block (Stereo) lautet:

Wenn Sie z. B. 128 Frames pro Block bei 48 kHz nutzen, ergibt das 128/48.000 ≈ 2,67 ms Blockzeit. Das ist für viele Anwendungen ein guter Startpunkt: überschaubare Latenz, dennoch ausreichend Luft für die CPU.

MPLAB Harmony: PLIB vs. Driver – welche Ebene ist die richtige?

In Harmony haben Sie grundsätzlich zwei Ebenen: PLIBs (Peripheral Libraries) für direkten Hardwarezugriff und Treiber, die eine höhere Abstraktion bieten. Für Audio ist das besonders relevant, weil sich I²S-Peripherien zwischen PIC32-Familien unterscheiden können. Microchip beschreibt, dass der I²S Driver diese Unterschiede abstrahiert und eine einheitliche Datenübertragung modelliert: Harmony: I2S Driver Library Help.

- PLIB-Ansatz: maximale Kontrolle, ideal für schlanke, dedizierte Audio-Firmware, erfordert aber tiefes Hardwareverständnis.

- Driver-Ansatz: schneller produktiv, portabler, oft mit sauberer DMA-Integration, dafür etwas mehr Overhead.

Für produktionsnahe Projekte ist der Treiberansatz häufig die bessere Startbasis. Sie können später noch auf PLIB optimieren, wenn Sie wirklich jeden Zyklus brauchen.

I²S-Formate: Standard I²S, Left-Justified, Right-Justified und PCM/DSP

In Audio-Projekten scheitert die Integration oft nicht an der Bitrate, sondern am Format. Viele Codecs unterstützen mehrere Modi. PIC32-Hardware bietet ebenfalls verschiedene Audio-Protokollmodi. Microchip nennt in der PIC32-Referenz explizit Unterstützung für I²S, Left/Right-Justified und PCM/DSP (geräteabhängig): PIC32 FRM: Audio Protocol Interface Mode (PDF).

- I²S (klassisch): WS wechselt typischerweise eine Bitclock vor dem MSB; Daten sind um 1 Bit versetzt.

- Left-Justified: MSB ist direkt an der WS-Flanke ausgerichtet.

- Right-Justified: LSB ist an einer definierten Stelle ausgerichtet (Codec-spezifisch).

- PCM/DSP: häufig TDM-ähnliche Rahmen, andere WS/Frame-Signale.

Wenn Sie „nur Rauschen“ oder „Kanäle vertauscht“ hören, ist das sehr häufig ein Format-Mismatch: Bit-Alignment, Word Length, Slot Length oder WS-Polung passen nicht.

Signalintegrität und Layout: Warum Audio über I²S trotzdem Hardware-Disziplin braucht

I²S ist eine digitale Schnittstelle, aber sie ist timingkritisch. Vor allem bei höheren BCLK/MCLK-Frequenzen sind saubere Flanken und stabile Bezugspotentiale entscheidend.

- Kurze Leitungen: BCLK und MCLK möglichst kurz und ohne unnötige Abzweige.

- Gute Masseführung: durchgehende Massefläche, Rückstrompfade nicht zerschneiden.

- Serienwiderstände (optional): kleine Dämpfungswiderstände nahe am Treiber können Ringing reduzieren.

- Trennung digital/analog: beim Codec Layoutbereiche für Analog (DAC-Ausgänge) und Digital (Clocks) sinnvoll trennen.

Viele „mysteriöse“ Audiofehler sind in Wahrheit Signalprobleme: MCLK overshoot, BCLK ringing oder schlecht entkoppelte Versorgung, die den Codec in Grenzbereiche bringt.

Audio-Verarbeitung auf dem PIC32: Von Gain bis DSP – realistische Erwartungen

Der PIC32 ist leistungsfähig genug, um typische Audioaufgaben in Echtzeit zu erledigen, wenn die Datenpipeline steht. Realistisch sind:

- Gain/Volume: Multiplikation pro Sample (mit Sättigung/Clipping-Regeln).

- Simple Filter: IIR (biquad) oder FIR mit moderaten Taps, abhängig von Takt und Blockgröße.

- Mixer: mehrere Quellen summieren, mit Headroom.

- Metering/Analyse: RMS/Peak, FFT blockweise (je nach CPU-Reserve).

Für „Profi-Niveau“ ist nicht nur der Algorithmus wichtig, sondern auch das numerische Format. 16-Bit-Audio lässt sich gut in 32-Bit-Akkumulatoren verarbeiten. Bei 24 Bit müssen Sie besonders auf Headroom achten, weil Summen schnell überlaufen. Eine typische Sättigungsstrategie ist, nach dem Mixen zu clampen, statt „wrap-around“ zu riskieren.

Skalierung und Headroom als Qualitätsfaktor

Wenn Sie zwei Vollaussteuerungs-Signale addieren, kann der Wertebereich theoretisch um den Faktor 2 steigen. Als Faustregel hilft eine Pegelreduktion vor dem Summieren, z. B. -6 dB (Faktor 0,5) pro Quelle bei einfachem 2-Kanal-Mix. In linearen Faktoren:

Das ist keine „universelle Wahrheit“, aber ein pragmatischer Startpunkt, um Clipping zu vermeiden.

Typische Fehlerbilder und schnelle Ursachenanalyse

- Kein Ton, aber Bus toggelt: falsches Format (I²S vs. Left-Justified), WS-Polung falsch, Codec nicht korrekt initialisiert.

- Knacksen/Dropouts: DMA-Buffer zu klein, ISR zu häufig, CPU-Lastspitzen, falsche Interruptprioritäten.

- Wandernde Kanäle/Phasenprobleme: LRCLK nicht stabil, falsche Slot-Länge, Bit-Shift um 1.

- Audio klingt „verzerrt“: falsche Wortbreite, fehlende Signextension bei 24 Bit, Überläufe ohne Sättigung.

- Nur bei niedriger Rate stabil: Signalintegrität, MCLK/BCLK-Flanken, Layout/Entkopplung, Codec-PLL instabil.

Wenn Sie den Eindruck haben, dass „an sich alles stimmt“, aber das System bei Parameterwechseln (z. B. Sample Rate) instabil wird, lohnt sich auch ein Blick in Community-Threads und Errata-Hinweise, weil Audio-Mode-Implementierungen in Einzelfällen besondere Randbedingungen haben können: Microchip Forum: PIC32MZ SPI/I2S Diskussion (Beispiel).

Praxisvorgehen: Stabil zum ersten sauberen Audio-Stream

- Codec-Setup zuerst klären: benötigte Clocks (MCLK?), Format, Word/Slot-Länge, Reset-Sequenz.

- I²S im Minimalmodus testen: nur Durchschleifen (Loopback) oder Testton, keine DSP-Logik.

- DMA/Ping-Pong aktivieren: Blockbasiert, mit konservativer Blockgröße starten.

- Format verifizieren: WS-Flanken, Bit-Alignment, Kanalzuordnung.

- Dann optimieren: Blockgröße, Latenz, Notification/Processing-Last, Signalqualität.

Ein strukturiertes Harmony-Umfeld hilft, weil Sie Treiber und PLIBs gezielt kombinieren können. Als Einstieg in Harmony-Dokumentation eignet sich die Microchip-Übersicht, die auch den Pfad zur offiziellen Harmony-Seite nennt: Harmony 3 Dokumentation (Microchip Support). Ergänzend bietet die Quick-Docs-Sammlung einen zentralen Einstieg in Treiber- und PLIB-Dokumente: MPLAB Harmony 3 Quick Docs.

Weiterführende Outbound-Links für belastbare Umsetzung

- Microchip Harmony: SPI-I2S Peripheral Library Help (PIC32MX/MZ)

- Microchip Harmony: I2S Driver Library Help (Abstraktion, Transfermodell)

- PIC32 FRM: SPI-Kapitel mit Audio Protocol Interface Mode (I²S, Left/Right Justified, PCM/DSP) (PDF)

- NXP: I2S Bus Specification (Timing und Grundlagen) (PDF)

- Microchip: Harmony 3 Dokumentation finden und nutzen

- MPLAB Harmony 3 Quick Documentation Package

- Microchip: PIC32 Peripheral Library (Einordnung und Hinweise zu Harmony)

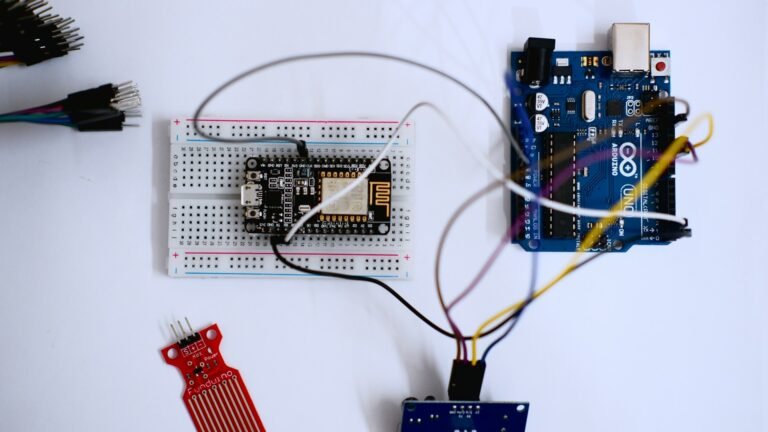

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.