Wer die SPI-Schnittstelle meistern möchte, kommt an einem Thema nicht vorbei: High-Speed-Datentransfer ist weniger eine Frage „SPI eingeschaltet – läuft“, sondern das Ergebnis aus sauberer Takt- und Moduswahl, robustem Chip-Select-Handling, sinnvoller Pufferstrategie und guter Signalqualität auf der Leiterplatte. Gerade am STM32 ist SPI oft die erste Wahl, sobald I2C zu langsam wird oder ein Bus mit deterministischen Timings benötigt wird – zum Beispiel für schnelle ADCs, externe Flash-Bausteine, Displays, Funkmodule oder Sensoren mit hohen Datenraten. SPI wirkt auf den ersten Blick simpel (SCK, MOSI, MISO, CS), doch hohe Geschwindigkeiten bringen typische Stolpersteine mit: falscher CPOL/CPHA-Modus, instabile Flanken durch zu lange Leitungen, unpassende Pull-ups oder fehlende Serienwiderstände, zu kleine DMA-Puffer, ineffizientes „Byte-weise Polling“ und Timing-Probleme bei Chip-Select. Dieses Tutorial zeigt Ihnen praxisnah, wie Sie SPI am STM32 so konfigurieren und betreiben, dass der Datendurchsatz hoch bleibt und die Kommunikation auch unter Last stabil funktioniert – von der elektrischen Basis über STM32CubeMX/STM32CubeIDE bis zu DMA-Workflows und Performance-Messung.

SPI-Grundlagen: Full-Duplex, Takt und Chip-Select

SPI (Serial Peripheral Interface) ist ein synchroner serieller Bus. Der Master liefert den Takt (SCK), und pro Taktflanke wird ein Bit übertragen. Typischerweise gibt es drei Daten-/Steuerleitungen und eine Chip-Select-Leitung pro Slave:

- SCK: Taktleitung vom Master zum Slave.

- MOSI: Master Out, Slave In (Daten vom STM32 zum Gerät).

- MISO: Master In, Slave Out (Daten vom Gerät zum STM32).

- CS/NSS: Chip Select (aktiviert genau einen Slave).

Wichtig: SPI ist full-duplex. Das bedeutet, dass beim Senden gleichzeitig empfangen wird. Auch wenn Sie „nur schreiben“, liest der Master trotzdem Bits ein (häufig Dummy-Daten). Und wenn Sie „nur lesen“, müssen Sie Takte erzeugen, indem Sie Dummy-Bytes senden.

Für einen Überblick zur SPI-Idee ist die Spezifikationsunabhängigkeit wichtig: SPI ist ein De-facto-Standard, kein offiziell standardisiertes Protokoll wie USB. Eine neutrale Einführung bietet beispielsweise: Serial Peripheral Interface (SPI) – Überblick.

SPI am STM32: Welche Peripherie gibt es und warum das relevant ist

Viele STM32-MCUs bieten mehrere SPI-Instanzen, teils mit zusätzlichen Features wie FIFO, DMA-Anbindung, CRC-Unterstützung oder besonderen Modellen für Audio (I2S). Zudem gibt es bei einigen Familien separate High-Speed-Interfaces für externe Speicher (z. B. Quad-SPI oder Octo-SPI), die für sehr hohe Flash-Durchsätze gedacht sind. Für klassischen High-Speed-Datentransfer zu Sensoren, Displays oder ADCs ist jedoch meist die normale SPI-Peripherie die richtige Wahl.

- Mehrere SPI-Ports: entkoppeln schnelle und langsame Geräte, reduzieren Buskonflikte.

- DMA-Unterstützung: entscheidend für hohen Durchsatz bei geringer CPU-Last.

- Flexible Framegrößen: 8 Bit, 16 Bit (je nach MCU/Peripherie), hilfreich für bestimmte Bausteine.

Für die Projekt- und Pin-Konfiguration nutzen viele Entwickler STM32CubeMX und STM32CubeIDE: STM32CubeMX und STM32CubeIDE.

Die entscheidende Einstellung: SPI-Modus (CPOL/CPHA) korrekt wählen

Der häufigste Grund für „SPI liefert Müll“ ist ein falscher Modus. SPI definiert, auf welcher Flanke Daten gültig sind und wie der Takt im Idle-Zustand aussieht. Das wird über CPOL (Clock Polarity) und CPHA (Clock Phase) beschrieben.

- CPOL: bestimmt, ob SCK im Leerlauf low oder high ist.

- CPHA: bestimmt, ob Daten auf der ersten oder zweiten Flanke übernommen werden.

Geräte-Datenblätter nennen den Modus häufig als „SPI Mode 0–3“ oder als Timing-Diagramm. Verlassen Sie sich nicht auf Annahmen: Ein Displaycontroller kann Mode 0 verlangen, ein ADC Mode 1, und ein Flash-Baustein Mode 3. Wenn Ihr Signal mit dem Logic Analyzer „gut aussieht“, aber die Bytes falsch sind, ist CPHA/CPOL die erste Stelle, die Sie prüfen sollten.

Chip-Select meistern: Warum NSS-Handling über Stabilität entscheidet

Chip-Select (CS/NSS) ist bei High-Speed-SPI kritischer als viele erwarten. Viele Slaves interpretieren die CS-Flanke als „Frame-Beginn“ und „Frame-Ende“. Wenn CS zu früh toggelt, entstehen Off-by-one-Bytes, verschobene Registeradressen oder unvollständige Transfers.

- CS low halten: über die gesamte Transaktion (Befehl + Adresse + Payload) hinweg.

- CS Timing beachten: manche Bausteine fordern Mindestzeiten zwischen CS-Flanke und erstem Takt.

- Mehrere Slaves: pro Slave eine eigene CS-Leitung (kein „teilen“, außer das Protokoll ist dafür ausgelegt).

- CS als GPIO vs. Hardware-NSS: Für flexible Transaktionen ist CS als GPIO oft die robustere Wahl.

In vielen STM32-Projekten ist CS als GPIO Standard, weil Sie dann beliebige Frame-Strukturen abbilden können. Hardware-NSS kann sinnvoll sein, wenn das Protokoll streng byteorientiert ist und die Peripherie den Slave sauber „taktet“, ist aber nicht immer die beste Lösung für komplexe Befehlssequenzen.

Taktrate richtig wählen: Nicht „so schnell wie möglich“, sondern „so schnell wie sicher“

Der STM32 kann SPI oft sehr schnell takten – doch das Ziel ist nicht die höchste mögliche SCK-Frequenz, sondern eine stabile Übertragung im realen Layout und mit dem realen Slave. Entscheidend sind:

- Maximale SCK-Frequenz des Slaves: im Datenblatt angegeben, oft abhängig von Versorgung und Temperatur.

- Signalqualität: Overshoot, Ringing, Flankensteilheit, Leitungsführung, Massebezug.

- STM32 Peripheral Clock: SPI-Takt wird aus APB/Kernel-Clock abgeleitet, über Prescaler.

Rechenhilfe: Theoretischer SPI-Durchsatz

SPI überträgt pro Takt in der Regel ein Bit pro Leitung (MOSI bzw. MISO). Bei 8-Bit-Frames lässt sich der theoretische Byte-Durchsatz ohne Protokoll-Overhead grob abschätzen als:

Hier ist die SCK-Frequenz in Hz und der theoretische Durchsatz in Bytes/s. In der Praxis reduzieren Befehlsbytes, Adressbytes, Dummy-Zyklen, CS-Gaps und Software-Latenzen die Nutzrate deutlich. Genau deshalb sind DMA und effizientes Framing so wichtig.

Hardware-Layout für High-Speed-SPI: Die Basics, die wirklich zählen

Bei hohen SPI-Frequenzen wird Ihre Leiterplatte Teil des Übertragungssystems. Selbst wenn die Logikpegel „digital“ sind, verhalten sich Leitungen wie Übertragungsstrecken. Das führt zu Reflexionen, Ringing und Signalüberschwingern – besonders bei langen Leitungen, Steckverbindern oder Dupont-Kabeln.

- Kurze Leitungen: SCK und Datenleitungen so kurz wie möglich.

- Sauberer Massebezug: durchgehende Ground-Plane, kurze Return-Paths.

- Serienwiderstand am SCK: häufig 22–47 Ω nahe am Master reduziert Ringing deutlich.

- Keine „Sternverkabelung“: SPI ist nicht für lange Bus-Topologien gedacht; wenn mehrere Slaves, dann mit kurzen Abzweigen.

- Saubere Versorgung: lokale Abblockkondensatoren am Slave, sonst „kippen“ Pegel bei Lastspitzen.

Wenn Sie High-Speed-Probleme vermuten, ist ein Logic Analyzer hilfreich, besser noch ein Oszilloskop, um Flankenform, Overshoot und Setup/Hold zu beurteilen.

STM32CubeMX: SPI korrekt konfigurieren (Pins, Prescaler, Framegröße)

In STM32CubeMX konfigurieren Sie SPI in wenigen Schritten, sollten aber bewusst entscheiden, welche Parameter wirklich zu Ihrem Slave passen:

- Master/Slave: STM32 ist in den meisten Anwendungen Master.

- Datenformat: 8 Bit ist Standard; 16 Bit kann bei bestimmten ADCs/Displays effizienter sein.

- Bitreihenfolge: MSB-first ist üblich, LSB-first selten (aber existiert).

- Prescaler: bestimmt SCK aus dem Peripherietakt; starten Sie konservativ und steigern Sie schrittweise.

- CPOL/CPHA: muss zum Slave-Datenblatt passen.

Die erzeugte Initialisierung ist ein Ausgangspunkt. Für echte Performance müssen Sie anschließend Ihr Transfermuster und die Pufferstrategie optimieren.

Polling vs. Interrupt vs. DMA: Der Weg zu echtem High-Speed

Viele Projekte starten mit Polling (blockierend): Byte senden, Flag prüfen, nächstes Byte. Das ist verständlich, skaliert aber schlecht. Sobald der Durchsatz steigt oder die CPU parallel andere Aufgaben hat (Sensorfusion, UI, RTOS, Kommunikations-Stacks), wird Polling zum Flaschenhals.

- Polling: gut für erste Tests, schlecht für hohe Datenraten und niedrige Latenz anderer Tasks.

- Interrupt: entlastet die CPU teilweise, aber bei sehr hohen Byte-Raten entsteht Interrupt-Overhead.

- DMA: ideal für große Transfers, weil der Datenstrom „hardwareseitig“ läuft und die CPU nur Start/Ende behandelt.

Für High-Speed-Datentransfer am STM32 ist DMA in der Praxis meist der entscheidende Schritt. Besonders bei Displays, externen ADC-Streams oder Speicherzugriffen kann DMA den Unterschied zwischen „ruckelt“ und „läuft dauerhaft stabil“ ausmachen.

DMA richtig nutzen: Puffer, Burst-Transfers und CPU-Entkopplung

DMA ist nicht automatisch schnell, wenn die Pufferstrategie schlecht ist. Entscheidend ist, dass Sie Transfers in sinnvolle Blöcke schneiden und die CPU-Arbeit minimieren.

- Große Blöcke statt Einzelbytes: reduzieren Setup-Overhead.

- Double Buffering: während DMA Buffer A sendet, berechnet die CPU Buffer B.

- Ringbuffer für RX: sinnvoll, wenn kontinuierlich Daten ankommen.

- Kurze ISRs: DMA-Complete-Callbacks sollten nur signalisieren, nicht „alles verarbeiten“.

Ein typisches Profi-Muster ist: DMA überträgt, ein Callback setzt ein Flag oder gibt ein Semaphore, und eine Task verarbeitet die Daten in Ruhe. So bleibt das System planbar.

SPI-Transaktionen strukturieren: Befehle, Adressen, Dummy-Bytes

Viele SPI-Geräte sprechen nicht „nur Daten“, sondern definieren Transaktionen: erst ein Kommando, dann eine Adresse, dann Daten – manchmal mit Dummy-Bytes dazwischen. High-Speed gelingt nur, wenn Sie diese Struktur effizient abbilden und CS korrekt halten.

- Kommandobyte: z. B. „READ“ oder „WRITE“.

- Adressbytes: 1–4 Bytes, abhängig vom Gerät.

- Dummy-Zyklen: nötig bei schnellen Flash-Bausteinen, damit der Slave Daten bereitstellen kann.

- Continuous Mode: manche Slaves erlauben das Lesen großer Blöcke ohne erneute Adressierung.

Wenn Ihr Transfer aus vielen kleinen Fragmenten besteht, verlieren Sie Zeit durch CS-Gaps und Funktionsaufruf-Overhead. Oft ist es besser, ein zusammenhängendes TX-„Header“-Buffer zu bauen und anschließend den Payload per DMA zu senden.

Mehrere Slaves am SPI: Bus-Design ohne Überraschungen

SPI ist für mehrere Slaves geeignet, wenn Sie es richtig verdrahten. SCK und MOSI können gemeinsam geführt werden, MISO ist gemeinsam nur dann unkritisch, wenn nicht aktive Slaves MISO wirklich hochohmig schalten. Viele tun das, manche Module oder Level-Shifter verursachen jedoch „MISO-Bus-Kämpfe“.

- Separate CS-Leitungen: pro Slave eine eigene Leitung, klar im Code gemanagt.

- MISO-Tri-State prüfen: Datenblatt des Slaves beachten; im Zweifel messen.

- Leitungsführung: kurze Abzweige zu den Slaves, keine langen „Kabelbäume“.

- Geschwindigkeit pro Slave: nicht jedes Gerät verträgt die gleiche SCK-Frequenz; per Prescaler umschalten.

Fehlerbilder verstehen: Warum SPI „manchmal“ geht

„Manchmal“ ist bei SPI fast immer ein Hinweis auf Signal- oder Timing-Probleme. Prototypen mit Dupont-Kabeln funktionieren bei 1 MHz, aber nicht bei 10 MHz. Oder ein Modus passt „halb“, sodass kurze Transfers zufällig korrekt sind, lange aber kippen.

- Bitfehler bei hoher SCK: Flanken zu schlecht, zu lange Leitungen, fehlender Serienwiderstand.

- Verschobene Bytes: CS falsch getoggelt, CPHA falsch, Dummy-Bytes fehlen.

- Nur Lesen oder nur Schreiben klappt: Full-Duplex nicht korrekt behandelt (Dummy-Bytes, RX-Drain).

- Störungen unter Last: CPU blockiert, DMA nicht genutzt, Interrupts zu lang, CS-Jitter.

SPI unter FreeRTOS: Mutex, „Single Owner“ und deterministische Transfers

Wenn mehrere Tasks SPI nutzen, ist Synchronisation Pflicht. Ein Mutex ist der einfache Weg, kann aber zu langen Blockaden führen, wenn große Display-Transfers laufen. In professionellen Systemen ist oft ein „Single Owner“-Pattern stabiler: Eine SPI-Task besitzt den Bus, andere Tasks stellen Requests in eine Queue, und die SPI-Task führt Transfers sequenziell aus.

- Mutex: schnell implementiert, aber auf Timeouts und Prioritäten achten.

- Single Owner: klare Steuerung, leichter zu debuggen, gut für gemischte Buslast.

- DMA + Event: Transfers starten, Completion signalisiert, Verarbeitung entkoppelt.

Wenn Sie grundsätzlich mit RTOS arbeiten, lohnt sich ein Blick in die FreeRTOS-Dokumentation, insbesondere zu Synchronisation und Task-Design: FreeRTOS Kernel Book.

Performance messen statt raten: Durchsatz, CPU-Last und Latenzen

High-Speed ist nur dann „gewonnen“, wenn Sie messbar schneller sind und dabei Ihr System stabil bleibt. Messen Sie daher:

- Durchsatz: Bytes pro Sekunde im echten Transfer (inklusive Protokoll-Overhead).

- CPU-Last: Polling vs. DMA ist hier meist ein großer Unterschied.

- Latenz: wie stark blockiert SPI andere Aufgaben (UI, Sensorfusion, Kommunikation)?

- Fehlerrate: bei steigender SCK-Frequenz beobachten (CRC, Plausibilität, Retry-Rate).

Bei Cortex-M-Kernen sind Debug- und Performance-Grundlagen gut bei Arm dokumentiert, unter anderem zu Debug/Trace-Konzepten: Arm Developer Documentation.

Best Practices: SPI am STM32 wirklich meistern

Wenn Sie High-Speed-Datentransfer am STM32 zuverlässig erreichen wollen, helfen einige bewährte Regeln, die sich in vielen Projekten wiederholen.

- Starten Sie konservativ: erst Mode/CS/Pinout stabil, dann SCK schrittweise erhöhen.

- Nutzen Sie DMA: für große Transfers und kontinuierliche Datenströme.

- CS bewusst managen: CS als GPIO ist häufig die robustere Wahl für komplexe Transaktionen.

- Layout zählt: kurze Leitungen, Ground-Plane, Serienwiderstand am SCK, saubere Versorgung.

- Transaktionen bündeln: weniger Fragmentierung, weniger Overhead, stabilere Timings.

- Mehrere Slaves sauber trennen: eigene CS-Leitungen, MISO-Tri-State prüfen, Takt pro Slave anpassen.

- Fehlerfälle einplanen: Timeouts, Retries, Plausibilitätschecks – besonders bei kritischen Daten.

Weiterführende Ressourcen

- STM32CubeIDE: Projekt-Setup, Build und Debug für STM32

- STM32CubeMX: Pinout, Clocks und Peripherie-Konfiguration

- Arm Developer Documentation: Cortex-M Debug- und Performance-Grundlagen

- FreeRTOS Kernel Book: Synchronisation und Task-Design

- SPI (Überblick) für Terminologie und Grundlagen

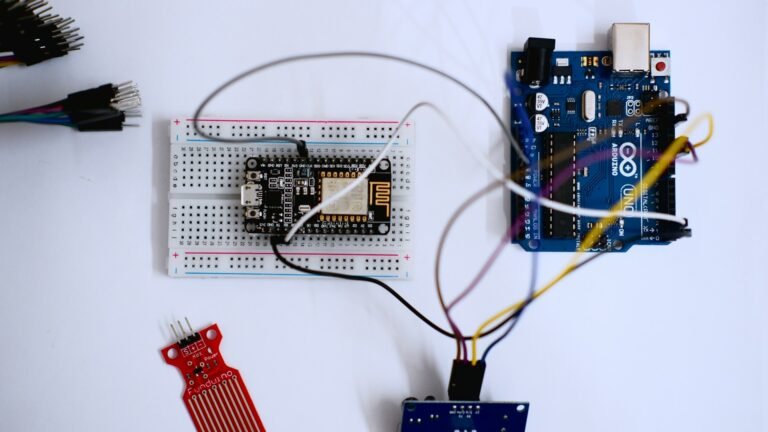

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.