Ein EMV-gerechtes Design für STM32-Platinen entscheidet oft darüber, ob ein Prototyp im Labor stabil läuft oder ob ein Produkt später im Feld sporadische Resets, Kommunikationsfehler, ADC-Rauschen oder unerklärliche Störungen zeigt. Gerade STM32-Mikrocontroller mit schnellen Flanken, hohen Taktfrequenzen, mehreren Versorgungsschienen und komplexen Peripherien (USB, CAN, Ethernet, SDMMC, Displays) sind anfällig für typische EMV-Probleme: zu große Stromschleifen, schlecht geführte Rückstrompfade, unzureichende Entkopplung, ungünstige Masseführung oder ein Layout, das empfindliche Analogsignale neben aggressiven Taktleitungen führt. Gleichzeitig ist EMV kein „Zauber“, sondern in vielen Fällen eine Folge weniger Grundregeln: Strom muss im Kreis fließen, schnelle Signalflanken erzeugen hochfrequente Spektralanteile, und jede Leitung ist in Wahrheit ein HF-Bauteil. Dieser Beitrag gibt Ihnen praxisorientierte Layout-Tipps für STM32-Platinen – von Layer-Stackup, Decoupling und Reset/Boot-Pins bis hin zu USB/Ethernet-Führung, ADC-Design, Schutzbeschaltungen und typischen Mess- bzw. Debug-Strategien. Ziel ist ein Design, das robust ist, reproduzierbar funktioniert und Ihnen spätere EMV-Feuerwehraktionen erspart.

EMV im Embedded-Design verstehen: Störquelle, Kopplung, Störopfer

EMV-Probleme lassen sich fast immer auf eine einfache Kette reduzieren: Eine Störquelle erzeugt Energie, diese koppelt über einen Pfad ein, und ein Störopfer reagiert darauf. In STM32-Designs sind typische Störquellen schnelle Takt- und Datenleitungen, Schaltregler, DC/DC-Wandler, GPIOs mit steilen Flanken oder hochfrequente Schnittstellen wie USB. Kopplungswege sind leitungsgebunden (z. B. gemeinsame Versorgung/ Masseimpedanzen) oder feldgebunden (kapazitiv/induktiv). Störopfer sind häufig Reset-Pin, Quarz-Oszillator, ADC-Eingänge, Referenzspannungen, empfindliche Sensorleitungen oder Kommunikationsschnittstellen.

- Leitungsgebunden: Störungen wandern über VDD/GND, IO-Leitungen oder Schirm/PE.

- Kapazitive Kopplung: Störspannung wird über parasitäre Kapazitäten eingekoppelt (nahe parallele Leiterbahnen).

- Induktive Kopplung: Störstromschleifen koppeln magnetisch ein (große Schleifenfläche).

- Abgestrahlt: Leitungen und Schleifen wirken wie Antennen, besonders bei hohen Flanken.

Für ein grundlegendes EMV-Verständnis (Begriffe, Abgrenzung, Mechanismen) ist eine kompakte Orientierung hilfreich: Electromagnetic compatibility (EMC) Überblick.

Layer-Stackup und Masseführung: Die wichtigste EMV-Entscheidung

Wenn Sie nur eine EMV-Regel konsequent umsetzen, dann diese: Eine durchgehende, zusammenhängende Massefläche unter den Signalen. Auf 4-Lagen-Boards ist ein typisches, robustes Stackup:

- Top: Signale + Bauteile (kurze Wege, kritische Netze oben)

- Layer 2: GND als durchgehende Referenzfläche

- Layer 3: Power (VDD-Schienen, ggf. Splits) und weniger kritische Signale

- Bottom: Signale (langsamer, weniger kritisch) + ggf. GND-Füllung

Eine durchgehende GND-Referenzfläche minimiert Rückstromschleifen. Der Rückstrom eines schnellen Signals fließt nicht „irgendwo“, sondern vorzugsweise direkt unter der Signalbahn entlang der kleinsten Impedanz. Schneiden Sie die Referenzfläche (z. B. mit Masse-Splits oder zu aggressiven Aussparungen), muss der Rückstrom ausweichen – die Schleifenfläche wächst, die Abstrahlung steigt, und Übersprechen nimmt zu.

Wann Masse-Splits sinnvoll sind und wann nicht

Die klassische „Analog-GND getrennt von Digital-GND“-Regel wird oft falsch angewendet. Trennung kann sinnvoll sein, wenn Sie klar definierte Strompfade und eine kontrollierte Kopplungsstelle (z. B. Sternpunkt) haben. Häufig ist jedoch eine gemeinsame, niedrige Masseimpedanz besser, plus gezielte Trennung der Ströme über Platzierung und Routing. Gerade bei modernen ADCs und Mixed-Signal-MCUs ist eine ungeschickte Massetrennung oft schlimmer als eine saubere gemeinsame Fläche.

Entkopplung am STM32: Kondensatoren richtig platzieren und routen

Entkopplung ist mehr als „ein paar 100 nF irgendwo“. Der Nutzen entsteht durch kurze, induktionsarme Verbindungen. Die kritische Größe ist nicht primär die Kapazität, sondern die Schleifeninduktivität der Strompfade zwischen VDD-Pin, Kondensator und GND.

- Pro VDD-Pin: Ein 100 nF (oder 47 nF) Keramik-Kondensator so nah wie möglich an den Pin.

- Mehrere Werte: Ergänzend 1 µF bis 4,7 µF in der Nähe des Controllers (Bulk nahe der Last).

- Kurze Rückführung: GND-Via direkt am Kondensator-Pad in die Massefläche (Via-in-Pad oder sehr nah).

- Eigene Schleife vermeiden: Nicht erst „über eine lange VDD-Schiene“ zum Kondensator.

Ein praktikables Daumenprinzip: Der Stromweg vom VDD-Pin zum Kondensator und zurück zur Masse sollte so kurz sein, dass er „wie ein kleines Dreieck“ wirkt – nicht wie ein Rechteck über mehrere Zentimeter.

Taktquellen und Quarzlayout: Der Oszillator ist ein EMV-Hotspot

Der Quarz- oder Resonatorbereich am STM32 ist empfindlich und zugleich eine potenzielle Störquelle. Falsches Layout führt zu Startproblemen, Jitter, erhöhter Abstrahlung oder zu sporadischem „Hängen“ bei Temperatur/Feuchte.

- Sehr kurze Leitungen: Quarz so nah wie möglich an die OSC-Pins.

- Symmetrisch routen: Beide Leitungen ähnlich lang und ohne unnötige Schleifen.

- Keine aggressiven Signale in der Nähe: Keine USB-Daten, keine PWM, keine schnellen GPIOs parallel.

- Ground-Guard: Optional GND-Ring/Guard um den Quarzbereich, ohne die Referenzfläche zu zerschneiden.

- Lastkondensatoren: Direkt am Quarz, mit kurzer GND-Anbindung.

Wenn Sie statt Quarz einen HSE-Oszillator (Clock-In) nutzen, ist die Leitung ebenfalls HF-kritisch: kurze Route, definierte Referenz, keine Via-Orgien.

Reset- und Boot-Pins robust machen: ESD, EMV und Fehlstarts vermeiden

NRST und Boot-Pins reagieren in vielen Designs empfindlich auf Störimpulse. Ein einzelner Burst kann zu Reset-Schleifen oder Boot in den falschen Modus führen.

- Pull-up/Pull-down korrekt dimensionieren: Boot-Pins nie „floaten“ lassen.

- RC-Filter für Reset: Oft sinnvoll, aber so auslegen, dass Debug/Programmierbarkeit erhalten bleibt.

- ESD-Schutz am externen Reset-Taster: Wenn der Pin nach außen geführt wird, TVS/ESD-Diode und saubere Rückführung.

- Leitung kurz und geschützt: NRST nicht quer über das Board neben Schaltreglerknoten führen.

RC-Zeitkonstante für Reset abschätzen

Wenn Sie einen Reset-Pin mit einem RC-Glied entstören (z. B. Pull-up

Als grobe Orientierung erreicht die Spannung nach etwa

Schaltregler und Versorgung: Das Layout entscheidet über Störpegel

Viele EMV-Probleme kommen nicht vom STM32 selbst, sondern vom Power-Design. Schaltregler erzeugen hohe dV/dt und dI/dt, vor allem am Schaltknoten (SW). Fehlerhafte Platzierung führt zu großflächigen Störfeldern und leitungsgebundenem Rauschen auf VDD.

- Hot-Loop minimieren: Eingangskondensator–Schalter–Diode/MOSFET–GND so kompakt wie möglich.

- SW-Knoten klein halten: Keine große Kupferfläche; Abstand zu sensiblen Signalen.

- Analogversorgung filtern: AVDD/VREF über LC oder Ferrit + lokale Entkopplung, wenn ADC empfindlich ist.

- Power-GND und Signal-GND verbinden: Niedrigimpedant, kontrolliert, keine „dünnen Brücken“.

Ein praxisnaher Einstieg in leitungsgebundene und abgestrahlte Störungen sowie typische Filtertopologien findet sich unter: Electromagnetic interference (EMI) Grundlagen.

Signalrouting: Rückstrompfade, Impedanz und saubere Referenzen

Für EMV ist nicht nur wichtig, wo die Signalleitung läuft, sondern auch, wo der Rückstrom fließt. Jede Via, jeder Layerwechsel und jede Unterbrechung der Referenzfläche kann den Rückstrom „umleiten“. Die Konsequenz sind größere Schleifen und mehr Abstrahlung.

- Signale über GND: Schnellere Signale bevorzugt über einer ununterbrochenen Massefläche routen.

- Layerwechsel mit Rückstrom-Via: Wenn ein Signal die Referenz wechselt, nahebei eine Stitching-Via setzen.

- Kurze, direkte Wege: Keine „Schlenker“, keine unnötigen Via-Kaskaden.

- Abstand und Parallelität: Lange parallele Strecken erhöhen Übersprechen – lieber Abstand oder orthogonales Routing auf benachbarten Lagen.

Warum Flankenzeit wichtiger ist als Taktfrequenz

Viele Entwickler denken nur in MHz, aber EMV-Probleme werden oft von ns-Flanken getrieben. Schnelle Flanken enthalten Spektralanteile weit oberhalb der Grundfrequenz. Eine grobe Beziehung zwischen Bandbreite

Das erklärt, warum selbst „langsame“ Signale mit sehr steilen Flanken EMV-Probleme verursachen können. In solchen Fällen helfen Serienwiderstände (Edge-Rate-Control) nahe am Treiber.

Serienwiderstände und Dämpfung: Edge-Rate-Control ohne großen Aufwand

Ein kleiner Serienwiderstand (typisch 22–47 Ohm) nahe am MCU-Pin kann Wunder wirken: weniger Ringing, weniger Überschwingen, geringere Abstrahlung. Das ist besonders hilfreich bei:

- SPI-Leitungen: SCK, MOSI, CS über längere Strecken.

- GPIO-Toggle-Signalen: schnelle Takt-/PWM-ähnliche Ausgänge.

- Display-Interfaces: parallele RGB oder schnelle SPI-Displays.

Wichtig: Serienwiderstände gehören möglichst nahe an den Treiber (STM32-Pin), damit die Flanke „entschärft“ wird, bevor sie die Leiterbahn als Antenne anregt.

USB am STM32: Differentialpair, ESD und Referenzfläche

USB ist EMV-kritisch, weil es schnelle Differentialsignale und strenge Signalqualität erfordert. Typische Layout-Regeln:

- D+ / D- als Differentialpaar: gleiche Länge, gleicher Bezug, konstante Geometrie.

- Keine Stubs: Keine Abzweige, keine Testpads als „Antennen“.

- Durchgehende Referenz: Unter dem Paar eine zusammenhängende GND-Fläche ohne Spalten.

- ESD-Schutz nahe am Stecker: TVS/ESD-Dioden mit kurzem Weg nach GND.

- Common-Mode-Filter optional: Kann EMV verbessern, muss aber zur Signalqualität passen.

Für die USB-Grundlagen und Signalcharakteristika ist die Spezifikationslandschaft umfangreich; ein erster Überblick ist hier hilfreich: USB Überblick.

Ethernet und schnelle Schnittstellen: Magnetics, Massebezug und Platzierung

Bei Ethernet-Designs (z. B. STM32 mit externem PHY) sind Magnetics und die Trennung von Chassis/Schirm und Signalmasse zentral. Typische EMV-Layoutpunkte:

- PHY nahe am RJ45/Magnetics: kurze MDI-Leitungen, saubere Impedanzführung.

- Referenzflächen kontrollieren: unter den schnellen Leitungen stabile Referenz, keine Masse-Splits.

- Schirmanbindung bewusst gestalten: Schirm/Chassis nicht „irgendwo“ an Signal-GND knoten, sondern mit definierter Strategie (z. B. kapazitiv/RC).

- ESD/Surge-Schutz: je nach Anwendung (Industrie) zusätzliche Schutzstufen vorsehen.

ADC, Sensoren und Analogteil: EMV-gerechte „Ruhezonen“ schaffen

Viele STM32-Projekte scheitern nicht an EMV-Tests, sondern an Messqualität: ADC-Werte springen, Offset driftet, Sensoren liefern Störungen, sobald PWM oder Funk aktiv ist. Die Ursache ist meist Kopplung über Masseimpedanz oder kapazitive Einkopplung.

- Analogbereich platzieren: Sensoren/Op-Amps/Referenz nahe an den ADC-Pins, weg von Schaltreglern und Taktleitungen.

- Separate Rückstrompfade: Analoge Ströme nicht durch digitale GND-Engstellen zwingen.

- RC-Filter an ADC-Eingängen: Anti-Alias/EMI-Filter direkt am Pin, mit definierter Quellenimpedanz.

- Referenzspannung sauber: VREF+ entkoppeln, kurze Leitung, keine „Shared“-Strompfade mit aggressiven Lasten.

Wenn Sie einen einfachen RC-Tiefpass am ADC-Eingang planen, können Sie die Grenzfrequenz

Das Filter hilft gegen hochfrequente Störungen, darf aber die ADC-Abtastung nicht verfälschen. Achten Sie daher auf Quellenimpedanz und Sample-and-Hold-Effekte.

ESD- und Transientenschutz: EMV beginnt am Stecker

Viele EMV-Probleme entstehen über die Außenwelt: ESD an Bedientasten, Burst/Surge über lange Leitungen, Störungen auf Versorgungskabeln. Layout-Tipps:

- Schutz nahe am Eintritt: TVS-Dioden und Filter möglichst direkt am Stecker, nicht erst „hinter dem Board“.

- Kurzer Ableitpfad: ESD-Strom muss schnell in eine geeignete Referenz (GND/Chassis) abfließen – lange Leiterbahnen erhöhen Spannungsspitzen.

- Getrennte Schutz-Masseführung: ESD-Ströme nicht durch empfindliche Signalmasse leiten.

- Filtertopologien: Ferrite, RC, LC je nach Interface (CAN, RS-485, GPIO, Versorgung).

Wenn Sie sich an normativen EMV-Familien orientieren möchten, ist IEC 61000 ein wichtiger Rahmen (Übersicht): IEC 61000 Überblick.

Routing-Checkliste speziell für STM32-Boards

- SWD-Header: kurze Leitungen, optional Serienwiderstände, saubere GND-Referenz, nicht neben USB-Daten.

- BOOT0/BOOT1: feste Pulls, keine langen Antennenleitungen, ggf. RC/ESD bei externen Schaltern.

- NRST: robust (Pull-up, optional RC), ESD bei externem Reset-Taster.

- VDDA/VREF: eigene Entkopplung, ruhige Platzierung, ggf. Ferrit von VDD trennen.

- Hochstrompfade: Motor-/LED-Treiber, Relais, DC/DC räumlich trennen und Rückstrompfad definieren.

- GPIO-Speed: unnötig hohe Slew-Rates vermeiden, wo möglich Edge-Rate-Control nutzen.

Mess- und Debug-Strategie: EMV-Probleme schneller eingrenzen

EMV-gerechtes Layout reduziert Probleme, ersetzt aber nicht das Messen. Typische, pragmatische Werkzeuge im Labor:

- Oszilloskop + Tastkopftechnik: kurze Massefeder statt langer Masseleitung, sonst messen Sie die Störung des Tastkopfs.

- Near-Field-Probes: für Hotspots (Schaltknoten, Taktbereiche, Rückstromengstellen).

- Strommessung: Shunt oder Stromzange, um Burst-Ereignisse und Resonanzen zu erkennen.

- Firmware-Hilfen: GPIO-Toggles zur Zeitmarkierung, Logging von Reset-Cause und Fault-Handlern.

Ein wichtiger Debug-Hinweis: Wenn Störungen „sporadisch“ auftreten, sind Reset-Ursachen (BOR, IWDG, WWDG, HardFault) Gold wert. Planen Sie schon im Layout Testpads und Messpunkte ein, aber vermeiden Sie dabei lange Stubs auf Hochgeschwindigkeitsleitungen.

Typische EMV-Fehlerbilder und passende Layout-Korrekturen

- USB disconnects / enumeration fails: Differentialpaar unterbrochen, ESD falsch platziert, Referenzfläche gesplittet, zu viele Vias.

- ADC rauscht bei PWM: Rückstrompfade nicht getrennt, Schaltregler zu nah, fehlender RC-Filter, ungünstige Masseengstellen.

- Random Resets: NRST/BOOT-Pins als Antenne, schlechte Entkopplung, Versorgungseinbruch, ESD/Burst über IO.

- CAN/RS-485 Fehler bei Motorbetrieb: fehlende Gleichtaktunterdrückung, schlechte Kabelschirmstrategie, unruhige Masseführung, unpassende Terminierung.

- Hohe Abstrahlung im EMV-Test: große Schleifen, gesplittete Referenzflächen, lange Taktleitungen, SW-Knotenfläche zu groß.

Outbound-Ressourcen für vertiefende EMV-Praxis

- Grundbegriffe zur elektromagnetischen Verträglichkeit (EMC)

- EMI-Mechanismen und typische Störquellen

- IEC 61000 als Normenfamilie für EMV

- USB-Grundlagen (Signalcharakteristika und Schnittstellenüberblick)

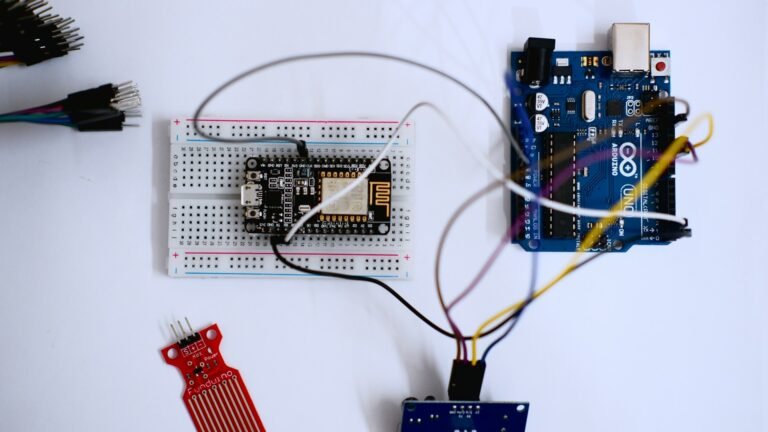

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.