Die Dual-Core Programmierung auf dem STM32H7 ist der Schlüssel, wenn Sie die Ressourcen dieser Mikrocontroller-Familie wirklich ausschöpfen möchten. Dual-Core-Varianten der STM32H7-Serie kombinieren typischerweise einen leistungsstarken Cortex-M7 für rechenintensive Aufgaben mit einem Cortex-M4 für energieeffiziente, echtzeitnahe oder peripherieorientierte Funktionen. Das eröffnet neue Architekturen: Während ein Kern die Datenakquise, Feldbuskommunikation oder Sicherheitsüberwachung deterministisch erledigt, übernimmt der andere Kern Signalverarbeitung, Regelalgorithmen, Netzwerk-Stacks oder grafische Benutzeroberflächen. Richtig umgesetzt, gewinnen Sie nicht nur „mehr Performance“, sondern vor allem bessere Systemtrennung, stabilere Latenzen und höhere Robustheit gegen Lastspitzen. Gleichzeitig ist Dual-Core-Entwicklung anspruchsvoller als Single-Core: Speicheraufteilung (DTCM/AXI/SRAM), Cache-Kohärenz, Inter-Core-Kommunikation, Boot- und Reset-Reihenfolge, Interrupt-Prioritäten sowie Debugging-Strategien müssen sauber geplant sein. Dieser Artikel erklärt praxisnah, wie Dual-Core-Programmierung auf dem STM32H7 funktioniert, welche Muster sich bewährt haben und wie Sie typische Fehler vermeiden, damit beide Kerne als echtes Team arbeiten.

Dual-Core-Architektur im STM32H7: Rollen von M7 und M4 verstehen

Im Dual-Core-STM32H7 übernimmt der Cortex-M7 meist die Rolle des „Performance-Kerns“: hohe Taktfrequenz, hohe Rechenleistung, gute Eignung für DSP, komplexe Zustandsautomaten, Netzwerk-Stacks und UI-Logik. Der Cortex-M4 ist häufig der „Echtzeit- und Peripherie-Kern“: Er kann Aufgaben übernehmen, die besonders deterministisch sein sollen oder bei denen Sie den M7 von Interruptlast entkoppeln wollen.

- Cortex-M7: rechenintensive Algorithmen, Filter/FFT, Ethernet/TCP/IP, GUI-Rendering, Datenkompression, komplexe Applikationslogik.

- Cortex-M4: präzise Zeitsteuerung, Sensor- und Aktor-Handling, Feldbus/Protokolle mit festen Deadlines, Sicherheits- oder Überwachungsaufgaben.

- Gemeinsam: Datenpipelines (Acquire → Process → Communicate), redundante Plausibilisierung, Lastspitzen abfedern.

Für eine offizielle Einordnung der STM32H7-Familie und ihrer Varianten ist die Produktübersicht zu STM32H7 bei STMicroelectronics ein sinnvoller Ausgangspunkt. Grundlegende CPU-Details lassen sich über die Architekturseiten zu Arm Cortex-M7 und Arm Cortex-M4 nachvollziehen.

Boot- und Startreihenfolge: Wer startet wen und warum?

Eine zentrale Frage in der Dual-Core Programmierung ist die Startreihenfolge: In vielen Designs startet der M7 zuerst, initialisiert Systemtakt, Speicher und grundlegende Ressourcen und „weckt“ dann den M4. Der Vorteil: Sie definieren eine klare Master-/Slave-Beziehung beim Boot und vermeiden, dass beide Kerne gleichzeitig dieselben Systemressourcen anfassen. Alternativ kann der M4 als „Always-on“-Kern genutzt werden, der minimal startet und später den M7 aktiviert, wenn mehr Leistung benötigt wird. Welche Variante sinnvoll ist, hängt vom Energieprofil, von Sicherheitsanforderungen und vom Reset-Verhalten im Feld ab.

- M7 als Master-Boot: klare Initialisierung, zentraler Systemtakt, strukturierter Start des M4.

- M4 als Supervisor: minimaler Start, Überwachung, Wakeup-Logik, M7 nur bei Bedarf aktiv.

- Wichtig: Reset- und Watchdog-Konzept so wählen, dass ein Kern den anderen nicht „in den Abgrund“ reißt.

Praktischer Hinweis zur Toolchain

Viele Teams nutzen STM32CubeIDE, weil sich Dual-Core-Projekte dort strukturiert anlegen lassen (zwei Projekte/Build-Targets, getrennte Linker-Skripte, koordinierte Debug-Konfiguration). Als Einstieg ist STM32CubeIDE hilfreich, weil dort auch die Einbindung von STM32Cube-Paketen und Debug-Workflows dokumentiert ist.

Speicheraufteilung: Warum Linker-Skripte bei Dual-Core alles sind

Die größte Fehlerquelle bei Dual-Core-Systemen ist eine unsaubere Speicheraufteilung. Beide Kerne sehen zwar „den RAM“, aber nicht jeder Speicherbereich eignet sich für jede Aufgabe. Typisch sind schnelle TCM-Bereiche (für deterministische Zugriffe) und größere AXI/SRAM-Bereiche (für Buffers, Stacks, Heap, Framebuffer). In Dual-Core-Designs müssen Sie festlegen, welche Bereiche exklusiv einem Kern gehören und welche Bereiche als Shared Memory dienen.

- Exklusiver Speicher pro Kern: Stack/Heap und zeitkritische Daten getrennt halten, um gegenseitige Störungen zu minimieren.

- Shared Memory: klar definierte Region für Inter-Core-Nachrichten, Ringbuffer oder Mailbox-Strukturen.

- MPU-Plan: Zugriffsschutz und Cache-Attribute pro Region festlegen, insbesondere für DMA und Shared Memory.

Cache-Kohärenz ist kein Detail, sondern ein Systemthema

Der Cortex-M7 arbeitet typischerweise mit Daten-Cache. Wenn der M4 auf Shared Memory zugreift, kann es passieren, dass der M7 alte Daten aus dem Cache liest oder neue Daten nicht rechtzeitig sichtbar werden. Deshalb müssen Sie für Shared Memory konsequent eine Strategie wählen:

- Shared Memory als non-cacheable: über MPU-Attribute; einfach und robust, kostet ggf. etwas Performance.

- Explizite Cache-Operationen: Clean/Invalidate vor/nach Zugriffen; leistungsfähig, aber fehleranfälliger.

- DMA-Puffer trennen: DMA und Inter-Core-Shared Memory nicht „wild“ mischen, sondern gezielt planen.

Inter-Core-Kommunikation: Von „Quick & Dirty“ zu robusten Mustern

Damit Dual-Core Programmierung den STM32H7 wirklich „voll ausreizt“, brauchen Sie eine zuverlässige Kommunikation zwischen M7 und M4. Die simpelste Variante ist ein paar Shared-Variablen im RAM – das funktioniert für Tests, skaliert aber schlecht. Professionelle Systeme nutzen klar definierte Kommunikationsmuster.

- Mailbox/Message Queue: Nachrichten mit Header (Typ, Länge, Sequenznummer), optional mit CRC oder Checksummen.

- Ringbuffer: gut für Streams (z. B. Sensorwerte), robust bei hoher Datenrate.

- Event-Flags/Semaphores: Signalisierung „Daten bereit“, „Ack erhalten“, „Zustand geändert“.

- RPC-ähnliche Calls: M4 bietet Dienste (z. B. Sensorread, IO), M7 ruft über definierte Requests auf.

Latenz und Durchsatz abschätzen

Für die Planung hilft eine einfache Zeitbudget-Betrachtung: Wenn ein Kommunikationszyklus aus tcopy (Daten kopieren), tsync (Synchronisation) und thandle (Verarbeitung) besteht, ist die maximale Nachrichtenfrequenz näherungsweise:

Das ist bewusst vereinfacht, macht aber sichtbar: Unnötige Kopien, zu feingranulare Nachrichten oder übermäßiges Locking ruinieren den Vorteil von zwei Kernen. Ziel ist, Kommunikation zu bündeln und pro Nachricht „mehr Arbeit“ zu transportieren.

Task-Splitting: Was gehört auf welchen Kern?

Die Kernfrage ist nicht „Was kann ich auf beide Kerne verteilen?“, sondern „Wie trenne ich das System so, dass es stabiler und deterministischer wird?“ Eine bewährte Methode ist, nach Zeitkritikalität und Datenrichtung zu trennen.

- Zeitkritische Peripherie-Pfade auf M4: ADC-Sampling, Timer-getriggerte IO, schnelle Protokolle, Schutzfunktionen.

- Rechenlast und variable Last auf M7: DSP, Kompression, Netzwerk, Dateisystem, UI.

- Kontrollierte Übergabe: M4 liefert „saubere“ Datenpakete, M7 verarbeitet blockweise und sendet Entscheidungen zurück.

Beispielmuster: Acquire → Process → Publish

Ein sehr robustes Dual-Core-Muster ist eine Pipeline:

- Acquire (M4): Sensoren lesen, Rohdaten in Ringbuffer, Timestamps setzen, Fehler prüfen.

- Process (M7): Filtern, Feature-Extraktion, Regelung/Entscheidung, Kompression.

- Publish (M7 oder M4): Daten über Ethernet/USB/CAN publizieren oder auf SD schreiben; je nach Latenzanforderung.

Dieses Muster reduziert Coupling: Der M4 bleibt deterministisch, der M7 darf „spiky“ sein (z. B. SD-Karte hat Schreibspitzen), ohne dass Daten verloren gehen – solange die Puffer dimensioniert sind.

RTOS oder Bare Metal: Zwei Kerne, zwei Betriebsmodelle

Dual-Core heißt nicht automatisch „zwei RTOS“. Sie können beide Kerne bare metal betreiben, nur einen Kern mit RTOS ausstatten oder beide mit getrennten RTOS-Instanzen laufen lassen. Die beste Wahl hängt von Teamkompetenz, Debugging-Anforderungen und den Echtzeitzielen ab.

- Beide bare metal: maximal deterministisch, minimaler Overhead, aber mehr Disziplin nötig (State Machines, Scheduling).

- M4 bare metal, M7 RTOS: häufig sehr praxistauglich: M4 macht harte Echtzeit, M7 verwaltet komplexe Tasks.

- Beide RTOS: gut skalierbar, aber Inter-Core-Synchronisation und Debugging werden anspruchsvoller.

Wenn Sie ein RTOS einsetzen, ist FreeRTOS eine verbreitete Basis, gerade in STM32-Projekten. Wichtig ist, dass Sie Inter-Core-Kommunikation nicht mit „RTOS-Magie“ verwechseln: Die Kerne sind getrennte CPUs, Synchronisation über Shared Memory muss weiterhin sauber gelöst werden.

Debugging und Trace: Dual-Core-Probleme sichtbar machen

Viele Dual-Core-Fehler sind Timing-bedingt: Race Conditions, verpasste Events, Cache-Effekte oder Deadlocks. Deshalb sollten Sie früh ein Debugging- und Logging-Konzept etablieren, das auf beiden Kernen konsistent funktioniert.

- Getrennte Logs: eigener Logkanal pro Kern (z. B. UART/RTT), plus Zeitstempel.

- Shared Debug-Buffer: Ringbuffer im Shared Memory, den ein Kern befüllt und der andere ausliest.

- Heartbeat-Mechanismen: jeder Kern liefert Lebenszeichen; Watchdog-Strategie erkennt Hänger gezielt.

- Event-Counter: Zähler für „Messages sent/received“, „Overruns“, „Timeouts“ – extrem hilfreich im Feld.

Single-Step ist selten aussagekräftig

Bei Dual-Core-Systemen führt Single-Stepping oft zu falschen Schlussfolgerungen, weil Timing-Interaktionen zerstört werden. Nutzen Sie stattdessen Logs, Counter, Trace-Pins oder periodische Status-Dumps. Besonders nützlich ist es, die Inter-Core-API so zu gestalten, dass sie diagnostisch ist: Jede Nachricht trägt eine Sequenznummer, jedes Ack bestätigt genau diese Nummer, Timeouts werden sichtbar.

Performance wirklich nutzen: Parallelisierung ohne Overhead

Der größte Gewinn entsteht nicht dadurch, beliebige Funktionen „irgendwie“ zu verteilen, sondern durch gezielte Parallelisierung entlang natürlicher Systemgrenzen. Ein guter Indikator ist die Amdahl-Logik: Nur der parallelisierbare Anteil profitiert, der Rest bleibt seriell. Als grobe Modellierung kann man den Speedup S so beschreiben:

Hier ist

Bewährte Anwendungsfälle: Wo Dual-Core auf dem STM32H7 besonders glänzt

- Industrial Gateway: M4 übernimmt Feldbus (CAN/CAN FD/RS-485) deterministisch, M7 macht Ethernet/TLS, Protokollkonvertierung und Web-UI.

- High-Rate-Datenlogger: M4 sampelt und puffert Sensoren, M7 komprimiert, schreibt auf SD (SDMMC) und streamt parallel.

- Motorsteuerung mit Diagnostik: M4 bedient ADC/PWM/Schutzlogik, M7 berechnet FOC/Observer und liefert Telemetrie.

- HMI-System: M4 übernimmt IO und sichere Zustände, M7 rendert GUI, verarbeitet Touch, verwaltet Daten.

- Edge-Analytics: M4 liefert Features in Echtzeit, M7 führt DSP/ML-Inferenz aus und veröffentlicht Ergebnisse.

Typische Stolpersteine und wie Sie sie vermeiden

- Unklare Ownership von Peripherie: definieren Sie eindeutig, welcher Kern welche Peripherie initialisiert und kontrolliert.

- Shared Memory ohne Cache-Strategie: Shared Regions entweder non-cacheable markieren oder Cache-Operationen standardisieren.

- Zu feingranulare Kommunikation: Nachrichten bündeln, Kopien reduzieren, Ringbuffer statt „Ping-Pong“ für Streams.

- Fehlende Timeouts: jedes Request/Response braucht Timeouts; Deadlocks sind sonst unvermeidlich.

- Debugging erst am Ende: Logs, Counter und Health-Monitoring von Anfang an integrieren.

Praktischer Entwicklungs-Workflow: So wird Dual-Core beherrschbar

- Phase 1: Kerne separat booten, „Hello World“ auf beiden Seiten, klare Speicheraufteilung im Linker.

- Phase 2: Inter-Core-Transport aufbauen (Shared Memory + Events), einfache Ping/Pong-Nachrichten mit Sequenznummern.

- Phase 3: Subsysteme trennen (z. B. M4 = I/O, M7 = Verarbeitung), Puffer- und Backpressure-Mechanismen definieren.

- Phase 4: Performance messen (Worst Case), Cache/DMA/MPU finalisieren, Robustheit mit Fault-Injection testen (Timeouts, Reset-Szenarien).

Wenn Sie Dual-Core-Programmierung als Architekturdisziplin verstehen – mit klarer Speicher- und Ownership-Planung, einer robusten Inter-Core-API und einer realistischen Performance-Strategie – lässt sich der STM32H7 tatsächlich „voll ausreizen“. Als verlässliche Startpunkte für Toolchain und Systemintegration bieten sich STM32CubeIDE und die Produktübersicht zu STM32H7 an, weil dort Dokumentation, Beispiele und Entwicklungswerkzeuge in einer konsistenten Umgebung zusammenlaufen.

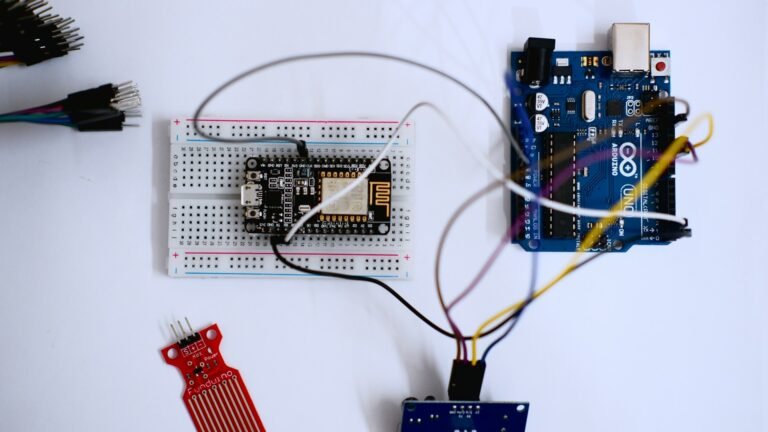

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.