Interrupts am PIC sind der Schlüssel, wenn Sie Ereignisse effizient verarbeiten und gleichzeitig echte Echtzeit-Eigenschaften erreichen möchten. Statt in der Hauptschleife ständig auf Zustandsänderungen zu warten („Polling“), reagiert der Mikrocontroller auf definierte Ereignisse sofort: ein Timer läuft ab, ein UART-Byte kommt an, ein Pin wechselt seinen Pegel oder ein ADC-Wandlungsergebnis ist fertig. Gerade bei PIC-Mikrocontrollern – ob PIC16, PIC18 oder verwandte Familien – entscheidet ein sauber aufgebautes Interrupt-Konzept darüber, ob ein System stabil, präzise und energiesparend arbeitet oder ob es bei Lastspitzen „zittert“, Daten verliert und unerklärliche Hänger produziert. In diesem Beitrag lernen Sie, wie Sie Interrupts am PIC als zuverlässige Ereignissteuerung einsetzen: von der Architektur (globale/periphere Interrupts, Prioritäten, Flags) über ISR-Designregeln (kurz, deterministisch, sicher) bis zu praktischen Mustern für Timer-Ticks, Kommunikationsschnittstellen und externe Ereignisse. Außerdem erfahren Sie, welche Stolperfallen besonders häufig sind – zum Beispiel falsch behandelte Flags, zu lange Interrupt-Routinen, fehlendes volatile oder nicht-atomare Zugriffe – und wie Sie diese Probleme systematisch vermeiden.

Warum Interrupts in Echtzeit-Systemen überlegen sind

Polling wirkt anfangs einfach: Sie prüfen in einer Schleife, ob ein Ereignis eingetreten ist. In kleinen Projekten kann das funktionieren. In Echtzeit-Systemen stößt Polling jedoch schnell an Grenzen, weil die Reaktionszeit vom Durchlauf der Hauptschleife abhängt. Je mehr Funktionen Ihr Programm enthält, desto länger dauert ein Loop – und desto später reagieren Sie auf wichtige Ereignisse. Interrupts lösen dieses Problem, weil sie den normalen Programmfluss kurz unterbrechen, sobald ein Ereignis auftritt.

- Geringere Reaktionszeit: Ereignisse werden zeitnah verarbeitet, unabhängig von der Länge der Hauptschleife.

- Deterministisches Verhalten: Mit sauberem ISR-Design lassen sich Worst-Case-Latenzen planen.

- Weniger CPU-Last: Die CPU arbeitet an Aufgaben, statt ständig Statusbits abzufragen.

- Energiemanagement: Schlafmodi werden praktikabler, weil Interrupts den PIC wecken können.

Ein pragmatisches Echtzeit-Ziel ist oft: „Ereignisse müssen spätestens nach X Mikrosekunden erkannt und verarbeitet werden.“ Interrupts sind der Standardmechanismus, um dieses Ziel planbar zu erreichen.

Interrupt-Architektur am PIC: Grundbegriffe, die Sie sicher beherrschen sollten

Die konkrete Interrupt-Struktur hängt von der PIC-Familie ab. Dennoch sind die zentralen Bausteine in vielen Geräten ähnlich: globale Freigabe, periphere Freigaben, Flag-Bits, Enable-Bits und (bei manchen Familien) Prioritäten.

Flag-Bit, Enable-Bit und globale Freigabe

- Flag-Bit: Zeigt an, dass ein Ereignis passiert ist (z. B. Timer-Overflow, UART RX).

- Enable-Bit: Erlaubt, dass dieses Ereignis einen Interrupt auslösen darf.

- Global Interrupt Enable: Schaltet das Interrupt-System insgesamt frei.

Ein häufiges Fehlbild ist: Das Flag ist gesetzt, aber der Interrupt kommt nicht – weil entweder das Enable-Bit oder die globale Freigabe fehlt. Umgekehrt kann ein Interrupt „dauerfeuern“, wenn das Flag im Handler nicht korrekt gelöscht wird.

Prioritäten: Wenn mehrere Ereignisse gleichzeitig eintreten

Einige PIC-Familien (z. B. viele PIC18) bieten Prioritäten (High/Low), andere arbeiten mit einem gemeinsamen Vektor und erfordern eine Software-Priorisierung im Handler. Prioritäten sind kein Selbstzweck: Sie sind sinnvoll, wenn Sie harte Echtzeit-Anteile (z. B. sehr kurze Timer- oder Kommunikationsfenster) gegenüber weniger kritischen Ereignissen bevorzugen müssen.

Die wichtigste Kenngröße: Interrupt-Latenz und Jitter

Für Echtzeit-Systeme zählt nicht nur „ob“ ein Interrupt kommt, sondern wann. Zwei Begriffe sind zentral:

- Latenz: Zeit zwischen Ereignis und Beginn Ihrer ISR.

- Jitter: Schwankung dieser Zeit (Varianz), z. B. durch blockierende Abschnitte oder konkurrierende Interrupts.

Die theoretische Untergrenze hängt vom Takt und vom Kern ab. Praktisch beeinflussen Sie Latenz und Jitter vor allem durch Ihr Software-Design: Wie lange sperren Sie Interrupts? Wie groß ist Ihr Kontextsave? Wie viel machen Sie in der ISR?

Ein einfacher Zusammenhang für Planung

Wenn Sie ein Zeitbudget in Instruktionszyklen abschätzen, hilft eine einfache Beziehung zwischen Frequenz und Periodendauer:

T = 1 f

Je höher der Takt f, desto kleiner die Zeit pro Zyklus T. Für eine robuste Echtzeit-Auslegung kombinieren Sie diese Abschätzung mit Messung (z. B. GPIO-Toggle am ISR-Anfang), um reale Latenzen zu verifizieren.

ISR-Designregeln: So bleiben Interrupts schnell und stabil

Die Interrupt Service Routine (ISR) ist der kritischste Codepfad im System. Jede unnötige Instruktion in der ISR kostet nicht nur CPU-Zeit, sondern verschlechtert die Reaktionsfähigkeit für alle anderen Ereignisse. Bewährte Regeln, die in professionellen Embedded-Projekten fast immer gelten:

- ISR kurz halten: Nur das Nötigste tun (Daten sichern, Flag setzen, Zähler erhöhen).

- Keine langen Schleifen: Keine Wartezyklen, keine blockierenden Routinen.

- Keine „schweren“ Funktionen: Kein printf, keine komplexe Protokollverarbeitung, keine Speicherverwaltung.

- Flags sauber löschen: Direkt und korrekt (geräteabhängige Mechanik beachten).

- Deterministisch bleiben: Verzweigungen und variabler Aufwand in der ISR erhöhen Jitter.

Ein sehr robustes Muster ist: ISR erfasst nur den Anlass und übergibt die Arbeit an die Hauptschleife (oder an einen Task-Mechanismus). Das nennt man häufig „deferred interrupt handling“.

volatile und atomare Zugriffe: Die häufigste Ursache für „Geisterfehler“

Wenn ISR und Hauptprogramm dieselben Variablen verwenden, müssen Sie dem Compiler deutlich machen, dass sich Werte „von außen“ ändern können. Sonst optimiert der Compiler vermeintlich unnötige Lesezugriffe weg.

volatile korrekt einsetzen

- Variablen, die in der ISR gesetzt und in der Main Loop gelesen werden, sollten in der Regel volatile sein.

- Gleiches gilt für Variablen, die in der Main Loop geschrieben und in der ISR gelesen werden.

Wichtig: volatile macht Zugriffe sichtbar, aber nicht automatisch „sicher“ im Sinne von Mehrbyte-Atomizität.

Mehrbytewerte atomar behandeln

Bei 8-Bit-PICs sind Zugriffe auf 16- oder 32-Bit-Variablen oft nicht atomar, weil sie aus mehreren Byte-Operationen bestehen. Ein Klassiker: Ein 16-Bit-Tickzähler wird in der ISR inkrementiert, während die Main Loop ihn gleichzeitig liest. Ergebnis: gelegentlich falsche Zwischenwerte.

- Option 1: Kurzzeitig Interrupts sperren, Wert kopieren, Interrupts wieder freigeben.

- Option 2: „Double-Read“-Muster: Wert zweimal lesen und vergleichen (wenn gleich, war es konsistent).

- Option 3: Zähler in Bytes abbilden und konsistent zusammensetzen.

Typische PIC-Interruptquellen und sinnvolle Einsatzmuster

PIC-Mikrocontroller bieten je nach Modell eine breite Palette an Interruptquellen. Für Echtzeit-Design sind besonders diese Gruppen relevant:

Timer-Interrupts: Die Zeitbasis des Systems

Timer-Interrupts sind ideal, um eine stabile Zeitbasis zu erzeugen, etwa einen 1-ms-Systemtick. Auf diesem Tick können Sie Software-Timer, Entprellung, Task-Scheduling oder Timeout-Überwachung aufbauen.

- Systemtick: ISR erhöht einen Zähler; Main Loop prüft und führt periodische Aufgaben aus.

- Edge-Zeitmessung: Timer als Zeitstempelquelle bei externen Ereignissen.

- PWM-Synchronisation: je nach Hardware auch für PWM-Updatepunkte relevant.

UART/USART: Datenverlust vermeiden

Bei serieller Kommunikation ist Interrupt-basierter Empfang oft die robusteste Variante, weil Sie eingehende Bytes sofort aus dem Hardware-Buffer holen können. Das reduziert das Risiko von Overrun-Fehlern, besonders wenn die Main Loop zeitweise beschäftigt ist. Ein gängiges Pattern ist ein Ringbuffer:

- ISR liest RX-Register und schreibt Byte in Ringbuffer.

- Main Loop verarbeitet den Ringbuffer und führt Protokolllogik aus.

- Fehlerflags (Overrun/Framing) werden in der ISR oder in einem klaren Fehlerpfad behandelt.

Externe Interrupts und IOC (Interrupt-on-Change): Schnelle Reaktion auf Pins

Für Taster, Encoder, Frequenzeingänge oder Zustandsänderungen sind externe Interrupts oder „Interrupt-on-Change“ (je nach PIC) nützlich. Wichtig ist hier das Thema Entprellung: Ein mechanischer Taster erzeugt Flankenfolgen, die ohne Filter viele Interrupts auslösen können. Entprellen Sie daher meist nicht in der ISR, sondern erfassen Sie nur den Zeitpunkt/Status und lassen Sie die Entprell-Logik in der Main Loop laufen.

ADC-Interrupt: Messwerte ohne Polling

Wenn ADC-Wandlungen periodisch oder ereignisgesteuert erfolgen, ist ein ADC-Interrupt eine saubere Lösung. ISR holt das Ergebnis, speichert es ab und setzt ein „neuer Messwert“-Flag. Die Auswertung (Filter, Skalierung, Grenzwertprüfung) sollte in der Regel außerhalb der ISR passieren, um Latenzen klein zu halten.

Priorisierung und Konflikte: Mehrere Interrupts gleichzeitig beherrschen

In Echtzeit-Systemen treten Ereignisse selten „schön nacheinander“ auf. Sie brauchen daher ein Konzept für Konflikte. Je nach PIC-Familie lösen Sie das durch Hardware-Prioritäten oder durch eine softwarebasierte Reihenfolge im gemeinsamen Handler.

Praktisches Prioritätsdenken

- Harte Echtzeit: kurze Fristen, z. B. Kommunikation oder präzise Timerfenster.

- Weiche Echtzeit: darf mal verzögert sein, z. B. Status-LED oder seltene Hintergrundaufgaben.

- Nicht zeitkritisch: Logging, Protokoll-Parsing, Berechnungen.

Wenn Ihre ISR spürbar wächst, ist das ein Warnsignal: Oft ist es besser, mehrere kleine Flags zu setzen und die Reihenfolge der Bearbeitung in der Main Loop zu definieren, statt die ISR zur „zweiten Hauptschleife“ werden zu lassen.

Interrupts in C mit XC8: saubere Struktur statt Copy-Paste

In XC8 definieren Sie Interrupt-Handler nach den Vorgaben des Compilers und der Zielarchitektur. Die exakte Syntax kann je nach Device-Familie variieren (z. B. einzelne Vektoren vs. zentrale ISR). Als belastbare Referenz lohnt sich die offizielle XC8-Dokumentation, weil sie die korrekte Einbindung in den Build und die Compiler-spezifischen Regeln erklärt: MPLAB XC8 Compiler.

- Eine zentrale ISR: Für viele Geräte üblich; dort prüfen Sie Flags in definierter Reihenfolge.

- Modulare Interrupt-Dispatcher: ISR ruft kurze Handler-Funktionen pro Peripherie auf (nur wenn extrem effizient implementiert).

- Flags zuerst lesen, dann löschen: abhängig vom Peripheral-Design; bei manchen Flags ist die Reihenfolge kritisch.

Ein stabiler Stil ist: „ISR prüft, erfasst, löscht, setzt Software-Flag.“ Die eigentliche Verarbeitung passiert in der Main Loop.

MPLAB Code Configurator (MCC) nutzen, ohne die Kontrolle zu verlieren

MCC kann Interrupt-Initialisierung und Treiber-Code generieren. Das spart Zeit, insbesondere bei Pin- und Peripheriekonfiguration. Dennoch gilt: Verstehen Sie, was generiert wird, und halten Sie Ihre Applikationslogik getrennt, damit sie nicht überschrieben wird. Als Einstieg in MCC und dessen Dokumentation eignet sich die offizielle Microchip-Seite: MPLAB Code Configurator (MCC).

- Nutzen Sie MCC, um Enable-Bits und Basiskonfiguration korrekt zu setzen.

- Platzieren Sie Applikationslogik nicht in generierten Dateien, sondern in eigenen Modulen.

- Überprüfen Sie nach jeder Regeneration, ob Flags/Handler weiterhin wie erwartet arbeiten.

Debugging und Verifikation: Interrupt-Probleme systematisch finden

Interrupt-Fehler sind oft schwer zu greifen, weil sie timingabhängig auftreten. Ein strukturiertes Vorgehen ist daher entscheidend.

Messbare Debug-Techniken

- GPIO-Toggle am ISR-Anfang: Mit Oszilloskop oder Logic Analyzer sehen Sie Latenz und Dauer der ISR.

- ISR-Dauer messen: Toggle am Anfang und Ende; Pulsbreite entspricht ISR-Laufzeit.

- Flags loggen: Software-Flags in einem Status-Byte sammeln, in der Main Loop per UART ausgeben (nicht in der ISR).

- Overrun- und Error-Flags prüfen: Bei UART/ADC/Timer sind Fehlerbits oft der eigentliche Hinweis.

Typische Symptome und ihre Ursachen

- ISR wird nicht aufgerufen: Enable-Bit oder globale Freigabe fehlt, falsche Vektor-/ISR-Signatur, falsches Device ausgewählt.

- ISR feuert ständig: Flag wird nicht korrekt gelöscht oder Ereignisquelle bleibt aktiv (z. B. Pin flackert).

- Gelegentliche Fehlwerte: nicht-atomare Mehrbyte-Zugriffe, fehlendes volatile, Race Conditions.

- Datenverlust bei UART: ISR zu langsam, Ringbuffer zu klein, Overrun nicht behandelt.

Stolperfallen vermeiden: eine praxisnahe Checkliste

- ISR niemals als Arbeitsroutine missbrauchen: Verarbeitung in die Main Loop verschieben.

- Alle relevanten Flags behandeln: Nicht nur das „Hauptflag“, sondern auch Error-Flags (Overrun, Framing, etc.).

- volatile konsequent: ISR/Main geteilte Variablen als volatile deklarieren.

- Atomizität sicherstellen: Mehrbytewerte geschützt kopieren.

- Interrupt-Sperren kurz halten: Lange kritische Abschnitte erzeugen Jitter und Datenverlust.

- Prioritäten bewusst wählen: Zeitkritisches vor weniger Kritischem (oder softwareseitig definieren).

- Hardware-Noise berücksichtigen: Flanken am Pin entprellen/filtern, sonst Interrupt-Stürme.

- Konfigurationsbits im Blick: Clock- und Debug-Einstellungen beeinflussen Timing und Verhalten.

Outbound-Links: Belastbare Referenzen für Interrupt-Workflows

- MPLAB X IDE (IDE-Workflow, Debugging, Projektkonfiguration)

- MPLAB XC8 Compiler (Compiler-Dokumentation und Toolchain-Details)

- MPLAB Code Configurator (MCC) (Peripherie-Setup, Codegenerierung)

- Configuration Bits in MPLAB X ansehen/setzen (Clock- und Debug-Fuses als häufige Timing-Ursache)

Ein leistungsfähiges Interrupt-Konzept am PIC entsteht aus klaren Rollen: Die ISR erfasst Ereignisse schnell und zuverlässig, die Hauptschleife verarbeitet sie geordnet und nachvollziehbar. Wenn Sie Latenz, Jitter, Atomizität und Fehlerflags konsequent im Blick behalten, wird aus „Interrupts irgendwie aktiv“ eine effiziente Ereignissteuerung, die Echtzeit-Systeme stabil trägt.

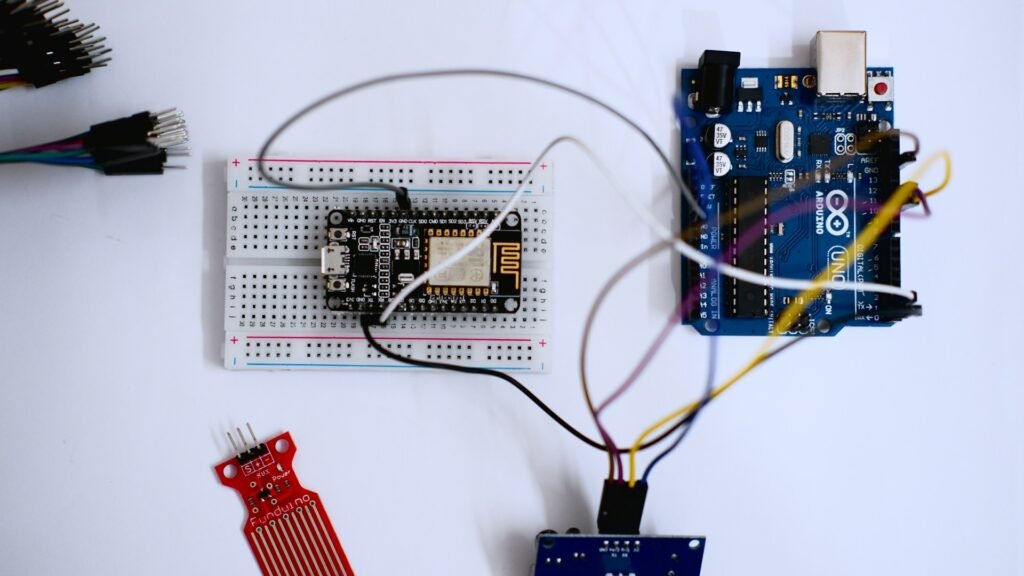

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.