Redundante Systeme mit PIC sind ein bewährter Ansatz, wenn in kritischen Anwendungen nicht nur Funktion, sondern auch Ausfallsicherheit, Verfügbarkeit und kontrolliertes Fehlverhalten gefordert sind. Während ein einzelner Mikrocontroller viele Aufgaben zuverlässig erledigt, entstehen in der Praxis Situationen, in denen ein Single-Point-of-Failure nicht akzeptabel ist: industrielle Sicherheitsfunktionen, Anlagen mit hohen Stillstandskosten, medizinische Teilfunktionen, Prozessüberwachung in rauen Umgebungen oder auch Infrastrukturkomponenten, die über Jahre ohne Wartung laufen müssen. Redundanz bedeutet dabei nicht automatisch „doppelte Hardware“ – sondern ein systematisches Konzept aus Architektur, Diagnose, Fehlererkennung, Fehlerisolation und definiertem Recovery. PIC-Mikrocontroller eignen sich für solche Konzepte besonders gut, wenn sie als deterministische Steuer- und Überwachungsinstanzen eingesetzt werden: als I/O-Controller, als unabhängiger Supervisor neben einem Hauptsystem oder als Teil einer zweikanaligen Logik mit gegenseitiger Plausibilisierung. Entscheidend ist, dass Redundanz nicht nur implementiert, sondern auch nachweisbar wirksam ist: durch klare Anforderungen, Teststrategien, Fehlereinbringung und eine saubere Dokumentation. In diesem Artikel erfahren Sie, welche Redundanzformen in der Praxis sinnvoll sind, wie Sie redundante PIC-Systeme robust auslegen und welche typischen Stolperfallen Sie vermeiden sollten.

Was bedeutet Redundanz in der Embedded-Praxis wirklich?

Im allgemeinen Sprachgebrauch ist Redundanz „eine zweite Instanz, falls die erste ausfällt“. In kritischen Anwendungen reicht diese Sicht jedoch nicht aus. Ein redundantes System muss Fehler nicht nur überstehen, sondern auch erkennen, isolieren und beherrschen. Sonst laufen zwei identische Fehler nur parallel weiter.

- Fehlererkennung: Wie erkennt das System, dass ein Kanal fehlerhaft ist (Timeout, Plausibilitätscheck, Selbsttest, CRC, Vergleich)?

- Fehlerisolation: Wie verhindert das System, dass ein defekter Kanal die anderen stört (Bus-Trennung, getrennte Versorgung, galvanische Entkopplung, sichere Default-Ausgänge)?

- Fehlerbeherrschung: Was passiert danach (Fail-safe, Fail-operational, Degradationsmodus, kontrollierter Reset, Umschaltung)?

Eine gute begriffliche Orientierung zu Redundanzkonzepten bietet ein technischer Überblick: Redundanz in technischen Systemen (Überblick). Für sicherheitsgerichtete Systeme ist außerdem die Normfamilie rund um funktionale Sicherheit ein wichtiger Kontext, z. B. IEC 61508 (Functional Safety).

Warum PIC-Mikrocontroller für redundante Architekturen häufig eingesetzt werden

In redundanten Systemen spielen PICs ihre Stärken vor allem dort aus, wo klare Zustandsmodelle, deterministische Zeitverläufe und robuste Peripherie gefragt sind. PICs werden häufig in Rollen eingesetzt, in denen sie nicht „alles“ tun müssen, sondern eine sicherheits- oder verfügbarkeitsrelevante Teilfunktion übernehmen.

- Supervisor/Housekeeping: Ein PIC überwacht Versorgung (BOR), Watchdog-Fenster, Temperatur, Kommunikationsheartbeats und setzt das Hauptsystem bei Bedarf kontrolliert zurück.

- Getrennter I/O-Kanal: Ein PIC liest Sensorik und steuert Aktorik unabhängig vom Hauptrechner; der Hauptrechner sendet nur Sollwerte, der PIC validiert Plausibilität.

- Zweikanalige Steuerung: Zwei PICs rechnen denselben Entscheid (z. B. Freigabe) und müssen übereinstimmen, bevor ein Ausgang aktiviert wird.

- Kommunikations-Gateway: Ein PIC bildet eine robuste, isolierte Schnittstelle (z. B. Feldbus zu interner Logik) und kann bei Fehlern in einen sicheren Modus wechseln.

Für Microchip-nahe Quellen zu Sicherheits- und Zuverlässigkeitsthemen lohnt sich ein Blick in das Microchip-Umfeld „Functional Safety“ und die dazugehörigen Ressourcen: Microchip Functional Safety (Übersicht).

Redundanzformen: Von Dual-Controller bis TMR

Redundanz ist nicht „one size fits all“. Welche Form sinnvoll ist, hängt von Risiko, Stillstandskosten, Diagnosefähigkeit und Komplexität ab. In der Praxis haben sich mehrere Muster etabliert.

1oo1, 1oo2, 2oo2: Entscheidlogik als Grundbaustein

In sicherheitsnahen Architekturen werden häufig „voting“-Logiken beschrieben: „one out of one“ (1oo1) ist ein Einzelkanal. „one out of two“ (1oo2) bedeutet, dass ein Kanal ausreicht, um eine Funktion auszulösen, während „two out of two“ (2oo2) verlangt, dass beide Kanäle zustimmen. Für PIC-Systeme sind diese Modelle praktisch, um Freigaben und Sperren zu definieren.

- 1oo2 (fail-operational Tendenz): Wenn ein Kanal ausfällt, kann der andere weiterarbeiten – birgt aber höhere Anforderungen an Diagnose, um Fehlfreigaben zu vermeiden.

- 2oo2 (fail-safe Tendenz): Bei Abweichung wird gesperrt; gut für sicherheitskritische Abschaltungen, aber weniger tolerant gegenüber einzelnen Fehlalarmen.

TMR (Triple Modular Redundancy): Dreifachredundanz mit Mehrheitsentscheid

Bei besonders kritischen Funktionen wird gelegentlich TMR eingesetzt: Drei Kanäle rechnen parallel, ein Mehrheitsentscheid bestimmt den Output. Für PIC-basierte Systeme ist TMR eher dort realistisch, wo die Funktion klein und klar ist (z. B. Freigabe-/Sperrlogik), weil Aufwand, Strombedarf und Komplexität deutlich steigen.

Fail-safe vs. Fail-operational: Das Ziel bestimmt die Architektur

Bevor Sie Hardware verdoppeln, sollten Sie definieren, was „Ausfallsicherheit“ konkret bedeutet. In kritischen Anwendungen gibt es zwei häufige Zielrichtungen:

- Fail-safe: Bei Fehler geht das System in einen sicheren Zustand (z. B. Aktor aus, Ventil zu, Motorstopp). Verfügbarkeit kann sinken, Sicherheit steigt.

- Fail-operational: Das System bleibt trotz eines Fehlers weiter funktionsfähig, zumindest eingeschränkt. Das verlangt deutlich mehr Diagnose und eine sichere Degradationsstrategie.

Viele PIC-Redundanzsysteme sind in der Praxis „fail-safe mit hoher Verfügbarkeit“: Sie vermeiden unkontrollierte Zustände, erlauben aber schnelle Recovery (z. B. Umschaltung auf einen Reservekanal, kontrollierter Neustart, Rückkehr in RUN nach Selbsttest).

Systemtrennung: Redundanz ist wertlos ohne Isolation

Ein verbreiteter Fehler ist „zwei Controller auf derselben Versorgung, denselben Taktquellen, denselben Signalleitungen“. Damit entsteht eine gemeinsame Fehlerursache (Common Cause Failure), die beide Kanäle gleichzeitig trifft. Gute Isolation bedeutet nicht zwingend komplette Verdopplung, aber klare Trennpunkte:

- Getrennte Versorgungspfade: idealerweise getrennte Regler, getrennte Entkopplung, definierte Brown-out-Schwellen.

- Getrennte Taktquellen: oder zumindest plausibilisierte Taktüberwachung, wenn eine gemeinsame Quelle genutzt wird.

- Physische Trennung kritischer Leitungen: um EMV-Einkopplungen und Kurzschlüsse zu entkoppeln.

- Bus-Isolation: getrennte I2C/SPI-Segmente oder Schutzmaßnahmen, damit ein defekter Teilnehmer den Bus nicht blockiert.

Gerade bei EMV-lastigen Umgebungen ist diese Trennung zentral, weil Spannungseinbrüche oder Störungen sonst beide Controller „gleichzeitig“ stören. Hier sind Konzepte wie Brown-out Reset (BOR), Watchdog und kontrollierte Startsequenzen unverzichtbar.

Diagnosemechanismen: So erkennt ein PIC, dass der andere spinnt

Redundanz lebt von Diagnose. Ohne Diagnose ist eine zweite Instanz nur eine zweite Fehlerquelle. In PIC-Systemen sind folgende Mechanismen besonders praxisnah:

- Heartbeat-Überwachung: Kanal A erwartet zyklisch ein Lebenszeichen von Kanal B (mit Timeout) und umgekehrt.

- Cross-Check von Ergebnissen: Beide Kanäle berechnen wichtige Größen (z. B. Grenzwertprüfung) und vergleichen.

- Plausibilitätsprüfungen: Sensorwerte, Zustände und Kommandos werden auf Grenzen und Konsistenz geprüft (z. B. Temperatur kann nicht in 10 ms um 20 °C springen).

- CRC/Signaturen: Firmware- und Datenintegrität wird geprüft, um Speicherfehler oder falsche Konfigurationen zu erkennen.

- Peripherie-Selbsttests: ADC-Referenz prüfen, RAM-Test beim Start, Kommunikationsloopback (wo möglich).

Windowed Watchdog als Anti-„Alibi-Kick“

In redundanten Systemen ist ein Watchdog sinnvoll, aber er muss korrekt integriert werden: nicht in einer schnellen Schleife, sondern als Ergebnis eines „gesunden“ Zyklus. Windowed-WDT-Ansätze verhindern, dass ein defekter Task den Watchdog permanent zu früh bedient. Das Prinzip verbessert die Fehlererkennung bei Deadlocks und Timing-Fehlern.

Umschaltstrategien: Warm Standby, Cold Standby, Hot Standby

Wenn ein Kanal ausfällt, muss klar sein, wie und wann umgeschaltet wird. Dabei unterscheiden sich die Betriebsarten vor allem in Reaktionszeit und Aufwand.

- Cold Standby: Der Reserve-PIC ist aus oder im tiefen Sleep und wird erst bei Fehler aktiviert. Sehr energieeffizient, aber längere Umschaltzeit.

- Warm Standby: Der Reserve-PIC läuft teilweise, hält Zustände vor, ist aber nicht voll aktiv. Guter Kompromiss.

- Hot Standby: Beide Kanäle laufen voll parallel, vergleichen sich und können sofort übernehmen. Höchste Verfügbarkeit, höchste Komplexität.

Für viele kritische Industrieanwendungen ist Warm Standby attraktiv: Der Reservekanal kann regelmäßig Selbsttests durchführen, seine Versorgung überwachen und hält eine minimale Zustandsinformation bereit, ohne permanent alle Lasten zu betreiben.

Ausgangsdesign: Redundanz endet nicht am Mikrocontroller-Pin

Ein redundant gerechneter Entscheid nützt wenig, wenn die Aktorik in einem Reset-Zustand unkontrolliert schaltet. Deshalb muss das Ausgangsdesign zur Redundanzstrategie passen. Typische Maßnahmen:

- Zweikanalige Freigabe: Ein Aktor erhält erst Strom, wenn zwei unabhängige Enable-Signale anliegen (z. B. von zwei PICs).

- Hardware-Verriegelung: Logikgatter, Safety-Relais oder Treiber-ICs, die bei Fehlern standardmäßig sperren.

- Fail-safe Defaults: Pull-downs/Pull-ups so wählen, dass ein Reset nicht zur Aktivierung führt.

- Strombegrenzung und Schutz: Kurzschluss- und Überstromschutz verhindert, dass ein Fehler eskaliert.

In sicherheitsrelevanten Domänen wird diese Denke über Normen wie ISO 26262 (Functional Safety – Road Vehicles) oder IEC 61508 strukturiert. Auch wenn Sie nicht formal zertifizieren, sind die Prinzipien (systematische Fehlervermeidung und zufällige Hardwarefehlerbeherrschung) als Engineering-Leitplanken sehr wertvoll.

Verfügbarkeit und Zuverlässigkeit abschätzen: Ein einfaches Modell

Für Entscheidungen über Redundanz hilft eine quantitative Näherung. Ein häufig verwendetes Maß ist die Verfügbarkeit A, die aus mittlerer Betriebsdauer bis zum Ausfall (MTBF) und mittlerer Reparatur-/Wiederherstellungszeit (MTTR) abgeleitet wird:

In Embedded-Systemen ist „Reparatur“ oft eine automatische Recovery (z. B. Reset, Umschaltung auf Reserve). Eine Redundanzarchitektur kann MTTR drastisch senken, weil das System schneller wieder einen definierten Betriebszustand erreicht. Gleichzeitig kann zusätzliche Komplexität die Ausfallrate erhöhen, wenn Diagnose und Isolation nicht sauber umgesetzt sind. Das Modell ist deshalb weniger als exakte Rechnung zu verstehen, sondern als Werkzeug, um die richtigen Fragen zu stellen: „Wie schnell komme ich zurück in RUN?“ und „Wie verhindere ich Common Cause Failures?“

Common Cause Failures: Der häufigste Grund, warum Redundanz scheitert

Common Cause Failures sind gemeinsame Ursachen, die mehrere Kanäle gleichzeitig treffen. In PIC-Systemen sind das häufig:

- Gemeinsame Versorgung: derselbe Regler, derselbe Puffer, dieselbe Masseführung.

- Gemeinsame Firmwarefehler: identischer Software-Bug in beiden Kanälen („Common Mode Failure“).

- Gemeinsame Sensorik: derselbe Sensor liefert falsche Werte; beide Kanäle entscheiden identisch falsch.

- Gemeinsamer Kommunikationsbus: ein blockierender Teilnehmer legt den Bus lahm.

Gegenmaßnahmen umfassen Diversität (unterschiedliche Implementierungen), unterschiedliche Sensorprinzipien, getrennte Versorgung, getrennte Taktdomänen sowie robuste Bus- und Fehlerbehandlung.

Diversität: Unterschiedlich ist oft sicherer als doppelt

Ein besonders wirkungsvoller Hebel in kritischen Anwendungen ist Diversität: Zwei Kanäle lösen dieselbe Aufgabe, aber nicht identisch. Das reduziert das Risiko, dass ein einzelner Bug beide Kanäle gleichzeitig trifft.

- Software-Diversität: getrennte Implementierung (z. B. anderer Algorithmus, anderer Zustandsautomat, andere Timingstrategie).

- Hardware-Diversität: anderer PIC-Typ oder anderes Sensormodul, sofern Beschaffung und Validierung es zulassen.

- Daten-Diversität: gleiche Messgröße mit zwei unterschiedlichen Sensorprinzipien (z. B. Druck + Durchfluss als Plausibilisierung).

Diversität erhöht Entwicklungsaufwand, kann aber in kritischen Anwendungen der entscheidende Unterschied zwischen „Redundanz auf dem Papier“ und echter Fehlertoleranz sein.

Test und Nachweis: Redundanz muss man kaputtmachen, um sie zu beweisen

Ein redundantes System ist erst dann belastbar, wenn Sie systematisch Fehler provozieren und die Reaktion messen. In der Praxis sind folgende Testarten besonders effektiv:

- Fault Injection in Hardware: Sensor abziehen, Leitung kurz stören, Versorgung kurz absenken, Bus blockieren.

- Fault Injection in Software: absichtliche Deadlocks, Timeout-Ausfälle, verfälschte Datenpfade (nur in Testbuilds).

- Umschalttests: Primärkanal resetten und prüfen, ob Reserve übernimmt, ohne unkontrollierte Ausgänge.

- Langzeittests: Dauerlauf mit Störereignissen und Logging (Reset-Cause, Umschaltzähler, Fehlerklassen).

Für reproduzierbare Ergebnisse hilft eine konsequente Dokumentation der Fehlerszenarien, der erwarteten Reaktion und des Nachweises. Auch wenn Sie nicht nach einer Norm zertifizieren, verbessert dieser Ansatz die Qualität und reduziert Feldprobleme.

Dokumentation nach E-E-A-T: Entscheidungen nachvollziehbar machen

Für Google-optimierten, vertrauenswürdigen Content und für reale Projekte gilt dasselbe Prinzip: Transparenz schafft Vertrauen. Beschreiben Sie bei redundanten PIC-Systemen nachvollziehbar:

- Welche Fehlerfälle werden abgedeckt? (Unterspannung, Software-Hänger, Sensorfehler, Bus-Timeout)

- Welche Redundanzform wird verwendet? (2oo2, 1oo2, Warm Standby, Supervisor-Architektur)

- Wie wird umgeschaltet? (Kriterien, Timing, sichere Zustände, Rückkehrstrategie)

- Wie werden Common Cause Failures reduziert? (Isolation, Diversität, getrennte Versorgung)

- Wie ist der Nachweis erbracht? (Tests, Fault Injection, Logs, Messungen)

Diese Struktur liefert nicht nur technischen Mehrwert, sondern stärkt die E-E-A-T-Signale, weil sie Expertise, Erfahrung und nachvollziehbare Engineering-Entscheidungen sichtbar macht.

Weiterführende Informationsquellen

- Grundlagen zu Redundanz in technischen Systemen: Redundanz (Technik)

- Funktionale Sicherheit als Rahmenwerk: IEC 61508 (Functional Safety)

- Automotive-Funktionssicherheit (Prinzipien auch außerhalb Automotive hilfreich): ISO 26262

- Microchip Ressourcen zu Functional Safety und Sicherheitskonzepten: Microchip Functional Safety

- Microchip Dokumentensuche für Datenblätter, Errata, Reset-/WDT-/BOR-Details: Microchip Dokumentensuche

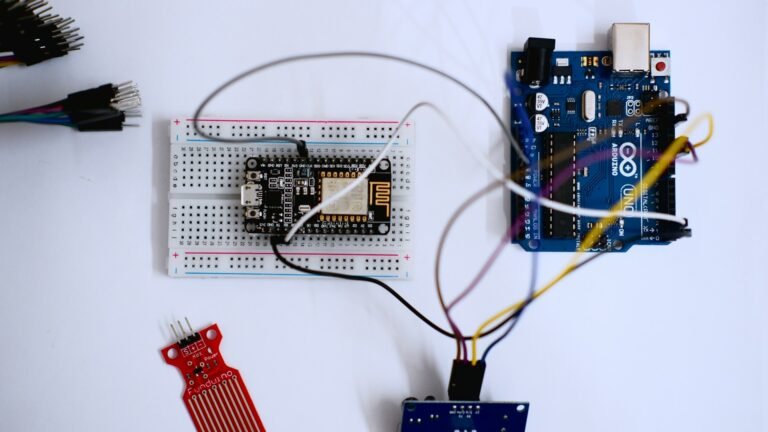

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.