Die RISC-V Architektur beim ESP32 ist mehr als ein technisches Detail – sie markiert einen strategischen Wandel, der sich in den kommenden Jahren spürbar auf Entwicklung, Produktplanung und die gesamte IoT-Landschaft auswirken kann. Während frühere ESP32-Generationen stark mit der Xtensa-Architektur verbunden waren, setzt Espressif bei mehreren neueren Familienmitgliedern auf RISC-V. Für Entwickler bedeutet das: ein offener, lizenzfrei nutzbarer Befehlssatz (ISA), eine wachsende Toolchain-Reife und potenziell mehr Transparenz und Portabilität im Embedded-Ökosystem. Gleichzeitig bleiben praktische Fragen entscheidend: Was ändert sich konkret beim Programmieren? Wie sieht es mit Performance, Energieverbrauch, Debugging und Security aus? Und wie beeinflusst der Architekturwechsel langfristig Frameworks wie ESP-IDF, die Community-Landschaft sowie neue Funk- und Smart-Home-Standards? Dieser Artikel ordnet die Bedeutung von RISC-V im ESP32-Universum ein, erklärt die technischen Hintergründe verständlich und zeigt, welche Auswirkungen auf die Zukunft realistisch sind – ohne Hype, aber mit klaren, praxisnahen Perspektiven.

RISC-V in einem Satz: Offener Befehlssatz statt proprietärer ISA

RISC-V ist eine offene Instruction Set Architecture (ISA), also ein standardisierter „Befehlssatz“, den Prozessoren implementieren können. Wichtig: „offen“ bedeutet nicht automatisch „Open Source“ für jeden Chip, wohl aber, dass die ISA als Grundlage unter offenen, dauerhaft verfügbaren Lizenzen bereitsteht und ohne klassische Lizenzgebühren oder Royalties für den Befehlssatz genutzt werden kann. RISC-V International beschreibt den Kernansatz als royalty-free und dauerhaft offen verfügbare Bausteine für Implementierungen und Erweiterungen. Wer den offiziellen Rahmen verstehen möchte, findet eine gut verständliche Einordnung direkt bei RISC-V International (About).

Welche ESP32-Chips sind RISC-V-basiert – und warum das relevant ist

Der Architekturwechsel ist bei Espressif nicht nur eine theoretische Option, sondern bereits Realität in mehreren Produktlinien. Ein prominentes Beispiel ist der ESP32-C3, dessen Datenblatt explizit einen 32-bit RISC-V Single-Core-Prozessor nennt. Damit wird deutlich: RISC-V ist nicht „Zukunftsmusik“, sondern bereits in verbreiteten, praxiserprobten SoCs angekommen. Als belastbare Referenz eignet sich das offizielle ESP32-C3 Datasheet.

Spannend wird es, wenn man den Blick auf modernere Funk- und Multiprotokoll-Anforderungen richtet. Beim ESP32-C6 nennt Espressif beispielsweise eine RISC-V-Architektur mit einem High-Performance- und einem Low-Power-Prozessor sowie die Integration von Wi-Fi 6 und 802.15.4 (relevant für Zigbee/Thread). Das ist ein Hinweis darauf, dass RISC-V nicht nur „ersetzt“, sondern auch die Plattform für neue Produktklassen und Systemarchitekturen bildet. Details finden sich auf der offiziellen Produktseite ESP32-C6 (Wi-Fi 6 & 802.15.4).

Warum Espressif auf RISC-V setzt: Strategie hinter der Technik

Bei Mikrocontrollern ist eine CPU-ISA nie nur eine akademische Entscheidung. Sie beeinflusst Toolchains, Debugger, Compiler-Optimierung, Drittanbieter-Bibliotheken, langfristige Wartbarkeit und das Recruiting von Embedded-Entwicklern. RISC-V bietet hier mehrere strategische Argumente:

- Unabhängigkeit und Standardisierung: Ein offener ISA-Standard kann die Abhängigkeit von proprietären ISA-Ökosystemen reduzieren.

- Breitere Toolchain-Basis: GCC/LLVM-Unterstützung für RISC-V ist breit, und viele Embedded-Tools wachsen um RISC-V-Targets.

- Skalierbarkeit: RISC-V ist modular (Base + Extensions). Hersteller können passende Erweiterungen nutzen, ohne den Standard zu brechen.

- Ökosystem-Dynamik: RISC-V wird in vielen Branchen vorangetrieben, was langfristig Druck in Richtung Reife und Stabilität erzeugt.

Wichtig ist dabei ein realistischer Blick: Ein offener ISA garantiert nicht automatisch, dass jede Implementierung „gleich“ ist. Mikroarchitektur, Peripherie, Memory-Map und SDK bleiben herstellerspezifisch. Trotzdem kann die gemeinsame ISA die Eintrittsbarriere senken – vor allem für Entwickler, die aus anderen RISC-V-Embedded-Ökosystemen kommen.

Was sich für Entwickler konkret ändert: Toolchain, Debugging und Portabilität

Viele ESP32-Projekte werden über das Espressif-Framework ESP-IDF entwickelt. Für die Praxis ist daher entscheidend, wie gut Compiler, Debugger, Build-System und Bibliotheken für RISC-V in dieser Umgebung funktionieren. Espressif bündelt die Entwicklungslogik in ESP-IDF und dokumentiert dort Treiber, Systemdienste und Build-Prozesse. Wer auf RISC-V-ESP32s umsteigt, sollte die IDF als „Single Source of Truth“ betrachten. Ein guter Ausgangspunkt ist die ESP-IDF Dokumentation.

- Build und Targets: RISC-V-basierte ESP32-SoCs nutzen andere Toolchain-Targets als Xtensa-SoCs, was sich in Build-Setups und CI-Pipelines bemerkbar macht.

- Debugging: RISC-V-Debugging ist in vielen Tools etabliert; dennoch hängt die tatsächliche Erfahrung stark von Board, JTAG-Setup und SDK-Version ab.

- Portabilität von Code: Reiner C/C++-Applikationscode ist häufig gut übertragbar; kritisch werden inline-Assembly, Timing-Tricks und herstellerspezifische HAL-Nutzung.

- Bibliotheken: Manche Low-Level-Bibliotheken sind ISA-abhängig (z. B. hochoptimierte DSP/crypto-Routinen) und müssen als RISC-V-Variante vorliegen.

Performance realistisch einordnen: ISA ist nicht gleich Geschwindigkeit

Ein häufiger Irrtum ist die Annahme, eine ISA bestimme direkt die Leistung. In Wirklichkeit hängt Performance von Takt, Pipeline, Cache, Memory-Subsystem, Peripherie-DMA und Optimierungsbibliotheken ab. Bei typischen IoT-Workloads (Sensorik, Protokolle, Steuerlogik) sind oft Netzwerk-Stacks und I/O das Nadelöhr, nicht die rohe CPU-ISA. Dennoch kann RISC-V die Optimierung erleichtern, weil Compiler-Tooling breit verfügbar ist und Hersteller gezielt Extensions oder beschleunigende Bibliotheken einsetzen können.

Für eine belastbare Betrachtung lohnt ein Blick in offizielle Datenblätter, da sie CPU-Takt, CoreMark-Werte und Memory-Ausstattung ausweisen. Beim ESP32-C3 werden beispielsweise CPU- und Performance-Kennzahlen im Datenblatt aufgeführt. ESP32-C3 Datasheet

Energieeffizienz und Low-Power-Design: Warum RISC-V hier indirekt zählt

Für batteriebetriebene IoT-Geräte ist Energieeffizienz zentral. Ob ein Gerät „monatelang“ läuft, wird in der Praxis jedoch weniger durch die ISA bestimmt, sondern durch das Gesamtdesign: Sleep-Modi, Aufwachstrategie, Funkzyklen, Sensor-Power-Gating und die Qualität der Stromversorgung. Dennoch kann eine moderne SoC-Architektur mit getrennten Power-Domains oder Low-Power-Kernen helfen, bestimmte Aufgaben im Sparmodus zu erledigen. Beim ESP32-C6 beschreibt Espressif beispielsweise eine Kombination aus High-Performance- und Low-Power-RISC-V-Prozessor. ESP32-C6 Produktdetails

Wer Laufzeitabschätzungen sauber dokumentieren will, kann das Prinzip über eine einfache Mittelwertbetrachtung ausdrücken. Das ist unabhängig von RISC-V, hilft aber, Energieentscheidungen nachvollziehbar zu machen:

Die Formel macht klar: Der entscheidende Hebel ist oft nicht „schnell rechnen“, sondern „kurz wach sein“.

Sicherheit und Trust-Features: Zukunftsfähigkeit hängt nicht nur am CPU-Kern

Bei IoT-Geräten ist Security nicht optional. Die ISA ist dabei nur ein Baustein. Entscheidend sind sichere Boot-Ketten, Flash-Verschlüsselung, Schlüsselmanagement, Update-Signaturen und eine robuste Firmware-Update-Strategie. RISC-V kann indirekt helfen, weil eine breitere Toolchain-Landschaft und Standardisierung die Sicherheitstests und Code-Audits vereinfachen können. Dennoch bleibt die konkrete Implementierung SoC-spezifisch und wird primär über die Espressif-Features im SDK und in den Hardware-Sicherheitsblöcken bestimmt.

- Langfristige Updates: Je länger Geräte im Feld bleiben, desto wichtiger sind reproduzierbare Builds und ein stabiler Updatepfad.

- Supply-Chain-Risiken: Ein standardisierter ISA-Ansatz kann Multi-Sourcing nicht garantieren, aber er kann die Portierung auf alternative RISC-V-Plattformen erleichtern.

- Auditierbarkeit: Offene ISA und starke Toolchains unterstützen statische Analyse, Fuzzing und reproduzierbare Build-Prozesse.

Ökosystem-Effekt: Mehr RISC-V bedeutet mehr Bibliotheken, Beispiele und Know-how

Die langfristige Bedeutung der RISC-V Architektur beim ESP32 zeigt sich im Ökosystem. Wenn eine wachsende Zahl an IoT-Chips auf RISC-V setzt, entstehen mehr Embedded-Beispiele, mehr optimierte Bibliotheken und mehr wiederverwendbares Know-how. Das kann die Entwicklung beschleunigen, weil Teams weniger „Sonderwissen“ für eine proprietäre ISA brauchen. RISC-V International betont die Offenheit und Dauerhaftigkeit der Standard-Lizenzierung – ein Argument, das vor allem für langfristige Plattformplanung zählt. RISC-V International

In der Praxis ist dennoch Vorsicht geboten: Die ISA ist nur die CPU-Ebene. Für ESP32-Projekte bleiben Funk-Stacks, Peripherietreiber und Board-Support weiterhin ein „Espressif-Universum“. Genau deshalb ist es sinnvoll, Projekte so zu strukturieren, dass Applikationslogik von Hardwarezugriff getrennt ist. Dann wird ein späterer Wechsel zwischen ESP32-Varianten (oder sogar zwischen Herstellern) realistischer.

Was bedeutet das für Arduino, MicroPython und Maker-Projekte?

Ein großer Teil der ESP32-Popularität kommt aus dem Maker- und Bildungsbereich. Dort zählen schnelle Erfolgserlebnisse, gute Beispiele und stabile Board-Pakete. RISC-V kann hier mittelfristig für mehr Konsistenz sorgen, weil viele Embedded-Toolchains ohnehin RISC-V-Targets unterstützen. Gleichzeitig hängt die Nutzererfahrung davon ab, wie schnell Board-Support, Libraries und Dokumentation nachziehen.

- Arduino-Ökosystem: Für viele Projekte bleibt Arduino attraktiv; die Qualität hängt von Core-Reife und Boarddefinitionen ab.

- MicroPython: Für Lehre und schnelle Prototypen ist MicroPython stark; Architekturfragen sind dort oft weniger sichtbar, solange Treiber stabil sind.

- Professionelle Migration: Wer langfristig plant, nutzt häufig ESP-IDF, um näher an den Systemfunktionen zu sein.

Wird Xtensa verschwinden? Ein realistischer Blick auf Übergangsphasen

Ein Architekturwechsel in einem erfolgreichen Ökosystem passiert selten „über Nacht“. Viele Bestandsprodukte, Bibliotheken und Toolchains sind über Jahre gewachsen. Deshalb ist es wahrscheinlich, dass Xtensa-basierte ESP32-Varianten noch lange parallel existieren – allein schon wegen bestehender Designs, Zertifizierungen und Produktionszyklen. Für Entwickler ist das kein Nachteil, solange sie die Plattformwahl bewusst treffen:

- Bestehende Produkte: Ein stabiles Xtensa-Design wird selten allein wegen RISC-V neu entwickelt, wenn es wirtschaftlich nicht nötig ist.

- Neue Designs: Bei Neuentwicklungen kann RISC-V attraktiver sein, wenn Funkstandards, Low-Power-Features oder Multiprotokoll-Anforderungen im Vordergrund stehen.

- Code-Strategie: Abstraktionsschichten und saubere Modulgrenzen reduzieren Migrationskosten zwischen Familien.

Welche Zukunftstrends RISC-V beim ESP32 besonders begünstigen kann

Die „Zukunft“ ist kein einzelnes Ereignis, sondern ein Bündel von Trends. RISC-V kann einige davon beschleunigen – vor allem dort, wo Standardisierung, Toolchain-Reife und Skalierbarkeit zusammenkommen.

- Multiprotokoll-IoT: Mehr Geräte müssen in gemischten Funkwelten arbeiten (WLAN, 802.15.4, BLE). Plattformen wie ESP32-C6 zeigen, wie stark sich SoCs in diese Richtung entwickeln. ESP32-C6

- Edge-Funktionalität: Mehr lokale Verarbeitung (Filter, Klassifikation, Event-Detektion), ohne Cloud-Abhängigkeit – RISC-V-Toolchains und Optimierungsbibliotheken profitieren davon.

- Langfristige Wartbarkeit: Offene ISA und breite Compiler-Unterstützung helfen, Code über Jahre sauber zu pflegen.

- Bildung und Workforce: RISC-V wird in Ausbildung und Forschung zunehmend genutzt; das kann die Verfügbarkeit von Know-how erhöhen.

Praktische Empfehlung für die Plattformwahl: So treffen Sie eine zukunftsfähige Entscheidung

Die beste Strategie ist selten „immer die neueste Architektur“, sondern „die passende Plattform für das Ziel“. Für zukunftsfähige Entscheidungen hilft eine klare Checkliste, die sowohl technische als auch organisatorische Faktoren berücksichtigt:

- Funkanforderungen: Brauchen Sie moderne WLAN-Features, 802.15.4 (Zigbee/Thread) oder nur klassisches 2,4-GHz-WLAN?

- Energieprofil: Netzbetrieb, Akku oder Energy Harvesting? Welche Wake-/Sleep-Strategie ist realistisch?

- Software-Stack: Reicht Arduino/MicroPython oder brauchen Sie ESP-IDF für Security, OTA, Debugging und CI?

- Langzeitpflege: Gibt es eine Update-Strategie und eine klare Versionspolitik?

- Teamkompetenz: Ist das Team eher Maker-orientiert oder produktionsnah mit Test- und Release-Prozessen?

Für eine fundierte, herstellernahe Basis sind die Espressif-Dokumentationen die verlässlichsten Referenzen: ESP-IDF für Entwicklungsprozesse sowie SoC-spezifische Produktseiten und Datenblätter wie ESP32-C3 Datasheet und ESP32-C6 für konkrete Hardwaremerkmale.

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

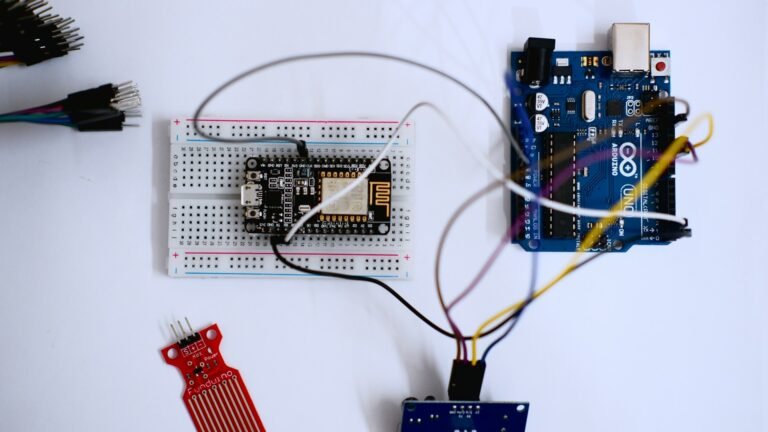

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.