RISC-V ist weit mehr als ein weiterer CPU-Befehlssatz: Die offene Architektur etabliert sich als strategische Alternative zu proprietären Plattformen und verändert damit, wie Chips entwickelt, lizenziert und langfristig eingesetzt werden. Während klassische Architekturen häufig an Lizenzmodelle, Patentportfolios und zentrale Anbieter gebunden sind, setzt RISC-V auf ein offenes, modular erweiterbares Konzept. Das senkt Einstiegsbarrieren, ermöglicht mehr Gestaltungsfreiheit und kann die Abhängigkeit von einzelnen IP-Lieferanten reduzieren. Für Unternehmen ist das attraktiv, weil sich Produkte differenzieren lassen – vom winzigen IoT-Controller bis zum Linux-fähigen SoC. Für Entwicklerinnen und Entwickler bedeutet es, dass Werkzeuge, Compiler, Betriebssysteme und Community-Wissen rund um RISC-V schnell wachsen. Gleichzeitig entstehen neue Fragen: Wo liegen die Grenzen der Offenheit? Wie kompatibel sind RISC-V-Implementierungen untereinander? Und warum sprechen viele von einer „Revolution“, obwohl der Markt seit Jahrzehnten von etablierten Ökosystemen dominiert wird?

Was ist RISC-V genau?

RISC-V (ausgesprochen „Risk Five“) bezeichnet eine offene Instruction Set Architecture (ISA) – also die formale Beschreibung der Maschinenbefehle, Register und grundlegenden Ausführungsregeln eines Prozessors. Wichtig ist die Unterscheidung: RISC-V ist nicht automatisch ein konkreter Chip, sondern die „Sprache“, die ein Prozessor versteht. Hersteller können darauf basierend eigene Kerne (Cores) entwickeln oder fertige RISC-V-IP einkaufen und in SoCs integrieren.

Als „offen“ gilt RISC-V, weil die ISA-Spezifikation öffentlich verfügbar ist und im Kern ohne klassische ISA-Lizenzgebühren genutzt werden kann. Wer tiefer einsteigen möchte, findet den offiziellen Rahmen bei RISC-V International sowie technische Details in den RISC-V ISA Manuals.

RISC vs. CISC: Warum der Name eine Rolle spielt

RISC steht für „Reduced Instruction Set Computer“: Das Designprinzip setzt auf einen vergleichsweise schlanken Befehlssatz und eine klare Pipeline-Orientierung. Moderne Prozessoren sind allerdings komplex, egal ob RISC oder CISC. Der praktische Vorteil von RISC-V liegt weniger in einem romantischen „weniger ist mehr“, sondern in der klaren, modularen Spezifikation: Basiserweiterungen und optionale Extensions lassen sich strukturiert kombinieren, ohne dass das Grundmodell ausufert.

Warum „offen“ den Markt verändert

In der Halbleiterwelt ist IP-Lizenzierung ein zentraler Kosten- und Machtfaktor. Wer eine proprietäre ISA nutzt, hängt typischerweise an Lizenzverträgen, Zertifizierungen, Roadmaps und Bedingungen eines Rechteinhabers. RISC-V verschiebt dieses Kräfteverhältnis: Unternehmen können eigene CPU-Kerne designen, optimieren und langfristig pflegen, ohne eine ISA-Lizenz als Flaschenhals. Das ist besonders relevant in Zeiten geopolitischer Unsicherheiten und Lieferkettenrisiken, in denen technologische Souveränität eine größere Rolle spielt.

- Geringere Eintrittsbarrieren: Start-ups und Forschungsteams können Prototypen schneller bauen.

- Mehr Differenzierung: Hersteller können Spezial-Extensions und Domain-spezifische Beschleuniger integrieren.

- Wettbewerb bei IP: Statt eines einzigen ISA-Anbieters konkurrieren viele Core- und Tool-Anbieter.

- Längere Produktzyklen: Unternehmen können unabhängiger von externen Lizenzänderungen planen.

Modularität: Das Herzstück von RISC-V

Ein zentraler Grund für den Erfolg ist die modulare Struktur. RISC-V definiert eine schlanke Basis (z. B. RV32I oder RV64I) und ergänzt diese über standardisierte Erweiterungen (Extensions). Dadurch kann ein Mikrocontroller sehr minimal bleiben, während ein leistungsfähiger SoC viele Features aktiviert.

Typische Standard-Extensions im Überblick

- M: Integer-Multiplikation und -Division (wichtig für viele Anwendungen).

- A: Atomare Operationen (relevant für Multicore, Locks, Betriebssysteme).

- F/D: Floating Point (Single/Double Precision), oft für Signalverarbeitung.

- C: Komprimierte Instruktionen (besserer Code-Dichte, hilfreich für Flash/Cache).

- V: Vektor-Erweiterung (für parallele Datenverarbeitung, HPC/AI/Media).

Für Entwickler ist das praktisch, aber auch eine Herausforderung: Nicht jeder RISC-V-Chip hat dieselben Extensions. Das macht eine saubere Zieldefinition beim Kompilieren und Testen wichtig.

RISC-V in der Praxis: Wo die Architektur bereits punktet

RISC-V ist in mehreren Segmenten attraktiv, weil er sich flexibel an die Anforderungen anpassen lässt. Besonders stark ist die Architektur dort, wo Stückzahlen, Kosten oder Anpassbarkeit dominieren.

- IoT und Mikrocontroller: schlanke Kerne, niedriger Energieverbrauch, gute Skalierbarkeit.

- Embedded Linux: SoCs mit MMU, gängigen Peripherieblöcken und Linux-Support.

- Beschleuniger und Co-Prozessoren: Custom Instructions und Domain-spezifische Designs.

- Forschung und Lehre: offene Spezifikation erleichtert Verständnis und Experimentieren.

Wer sich für den Software-Stack interessiert, findet einen guten Einstieg über das Linux-Kernel-Projekt, das RISC-V seit Jahren als Architektur unterstützt, sowie über GCC und LLVM als zentrale Compiler-Infrastruktur.

Ökosystem und Toolchain: Der entscheidende Erfolgsfaktor

Eine Architektur gewinnt nicht durch Papier, sondern durch Werkzeuge, Dokumentation und Entwickler-Community. RISC-V hat hier große Fortschritte gemacht: Cross-Compiler, Debugger, Simulatoren, Betriebssysteme, RTOS und Build-Systeme sind verfügbar. Für viele Teams ist das inzwischen „gut genug“, um ernsthafte Produkte zu entwickeln.

- Compiler: RISC-V Backends in GCC und LLVM, inklusive Optimierungen.

- Debugger: GDB-Unterstützung sowie JTAG/SWD-Workflows je nach Hardware.

- RTOS/Embedded: Unterstützung in gängigen RTOS-Stacks und Bare-Metal-Umgebungen.

- Linux-Userland: Tooling für Cross-Compilation, RootFS, Paketierung.

Ein Praxisvorteil: Viele Tools sind „upstream“ integriert, also Teil der offiziellen Projekte, statt in exotischen Forks zu leben. Das reduziert Wartungskosten in langfristigen Produkten.

Kompatibilität und Fragmentierung: Die offene Kehrseite

Offenheit kann Vielfalt fördern – und Vielfalt kann in Fragmentierung kippen. Bei RISC-V ist das Thema kompatible Software besonders wichtig, weil Hersteller unterschiedliche Extension-Sets, Speicher-Subsysteme und Peripherie-Designs kombinieren. Die ISA selbst ist standardisiert, aber die konkrete Plattform (Board/SoC) ist es oft nicht.

- Unterschiedliche Extensions: Code kann auf einem Core laufen, auf einem anderen aber nicht (z. B. fehlendes „C“ oder Floating Point).

- Plattform-Details: Interrupt-Controller, Timer, Boot-ROM und Device-Tree-Setups unterscheiden sich.

- Toolchain-Targets: Build-Flags und ABI-Settings müssen sauber gewählt werden.

In der Praxis lösen Teams das durch klare Zielprofile („baseline“) und durch Continuous Integration auf echter Hardware. Für Linux-Systeme spielen außerdem Standards rund um Device Tree eine wichtige Rolle; einen Einstieg bietet die Device-Tree-Dokumentation im Linux-Kernel.

Performance, Energieeffizienz und Kosten: Was RISC-V realistisch leistet

RISC-V ist keine magische Abkürzung zu höherer Performance. Die Leistungsfähigkeit hängt vom konkreten Core-Design, der Pipeline, den Caches, der Fertigungstechnologie und dem Gesamtsystem ab. Dennoch kann RISC-V in vielen Fällen sehr konkurrenzfähig sein – vor allem, weil Hersteller gezielt optimieren dürfen, ohne sich an einen ISA-Anbieter binden zu müssen.

- Performance: stark abhängig von Microarchitektur, Out-of-Order-Designs und Cache-Hierarchie.

- Energieeffizienz: gute Optionen für Low-Power-Designs, besonders in Microcontroller-Klassen.

- Kostenstruktur: potenziell geringere Lizenzkosten, aber Engineering-Aufwand bleibt real.

Wer RISC-V einsetzt, sollte also nicht nur „billiger“ erwarten, sondern vor allem „kontrollierbarer“: Roadmaps, Feature-Sets und Sicherheitsmaßnahmen lassen sich stärker in die eigene Hand nehmen.

Sicherheit und Trust: Was „offen“ für Security bedeutet

Offene Spezifikationen erleichtern die Überprüfbarkeit: Sicherheitsforscher können ISA-Details, Privilege-Modelle und Memory-Protection-Mechanismen unabhängig analysieren. Gleichzeitig kann Offenheit nicht verhindern, dass Implementierungsfehler in konkreten Cores oder SoCs auftreten. Security hängt am Ende an Designqualität, Verifikation, Secure Boot, Update-Strategie und Supply-Chain-Kontrolle.

- Positiv: Transparenz der Spezifikation, potenziell bessere Audits.

- Herausforderung: viele Implementierungen im Markt mit unterschiedlichem Reifegrad.

- Praxis: Secure Boot, Signaturprüfung und solide Key-Management-Prozesse bleiben Pflicht.

Gerade im Embedded- und IoT-Umfeld ist ein belastbarer Update-Mechanismus entscheidend – unabhängig von der CPU-Architektur. RISC-V ändert hier nicht die Grundregeln, kann aber durch die freie Gestaltung der Plattform Sicherheitskonzepte erleichtern.

RISC-V vs. ARM und x86: Ein fairer Vergleich

RISC-V wird häufig als direkte Konkurrenz zu ARM und im weiteren Sinne zu x86 dargestellt. Tatsächlich spielen die Architekturen in unterschiedlichen Stärken: ARM dominiert viele Embedded- und Mobile-Segmente durch ein extrem reifes Ökosystem, umfangreiche IP-Optionen und bewährte Toolchains. x86 ist im PC- und Serverbereich stark, vor allem durch Software-Kompatibilität und jahrzehntelang gewachsene Plattformstandards.

- ARM: sehr reif, enorme Auswahl an Cores und SoCs, starke Industrieprozesse – aber lizenzgebunden.

- x86: Plattformstandard im PC/Server, starke Legacy-Kompatibilität – aber weniger flexibel für Custom-SoCs.

- RISC-V: maximale Anpassbarkeit und Offenheit – aber heterogener, mit noch wachsendem Plattformstandard.

In vielen Fällen ist RISC-V nicht „besser“, sondern „anders“: Wer die Differenzierung über Hardware-Features, langfristige Unabhängigkeit oder spezielle Beschleuniger sucht, kann stark profitieren.

Industrie, Forschung und Politik: Warum RISC-V strategisch wird

RISC-V ist auch deshalb so relevant, weil Halbleiter als Schlüsseltechnologie gelten. Unternehmen und Institutionen möchten Abhängigkeiten reduzieren und Kompetenzen im eigenen Raum aufbauen. Eine offene ISA erleichtert es, Wissen aufzubauen und in Produkten umzusetzen, ohne an eine einzelne Lizenzquelle gebunden zu sein. Parallel treiben Forschungsprojekte, Hochschulen und Open-Source-Communities die Innovation voran, was wiederum Industrieadoption erleichtert.

Wer einen strukturierten Überblick über die RISC-V-Organisation und deren Arbeitsgruppen sucht, findet ihn bei RISC-V International (Überblick und Struktur). Für technische Einordnung der ISA und ihrer Varianten sind die offiziellen ISA-Handbücher eine der verlässlichsten Quellen.

Typische Einsatzszenarien für Entwickler und Maker

Auch im Maker- und Embedded-Bereich wird RISC-V immer sichtbarer, etwa in Entwicklungsboards und günstigen Mikrocontrollern. Der Mehrwert zeigt sich vor allem in Lern- und Experimentierprojekten: Man kann tiefer in CPU-Grundlagen einsteigen, ohne proprietäre Schranken. Gleichzeitig sollte man realistisch bleiben: Für Einsteiger ist nicht jedes RISC-V-Board automatisch „einfacher“ als ein etabliertes Arduino- oder ARM-Ökosystem. Entscheidend sind Dokumentation, Bibliotheken und Community-Support des jeweiligen Boards.

- Bare-Metal-Projekte: ideal zum Verständnis von Start-up-Code, Interrupts und Registerzugriff.

- RTOS-Projekte: gut für Task-Scheduling, Timing und Treiberentwicklung.

- Embedded Linux: sinnvoll, wenn Netzwerk-Stacks, Webserver oder komplexe Software laufen sollen.

Wie Sie RISC-V sinnvoll evaluieren

Wenn Sie RISC-V im Unternehmen oder für ein anspruchsvolleres Projekt bewerten, lohnt sich ein systematischer Ansatz. Dabei sollte die Entscheidung nicht nur auf „offen“ oder „Trend“ basieren, sondern auf messbaren Kriterien.

- Software-Stack: Welche Compiler-Versionen, Debug-Tools und Libraries sind produktionsreif verfügbar?

- ISA-Profil: Welche Extensions benötigen Sie, und sind diese auf dem Zielchip garantiert vorhanden?

- Langzeit-Support: Gibt es eine Roadmap, Sicherheitsupdates, dokumentierte Errata und stabile Lieferfähigkeit?

- Ökosystem: Existieren Referenzdesigns, Community-Beispiele, BSPs und gute Dokumentation?

- Compliance: Welche Zertifizierungen oder Normen sind in Ihrer Branche relevant (Safety, Security, EMV)?

Gerade in produktnahen Anwendungen ist außerdem die Verfügbarkeit von verlässlichen Referenzen und Spezifikationen wichtig – hier helfen die Primärquellen: GCC, LLVM und Linux Kernel zeigen, wie tief RISC-V in der Werkzeuglandschaft inzwischen verankert ist.

Lizenzmodelle, IP und „offen“ im Detail

In der Praxis bedeutet „offen“ bei RISC-V vor allem: Die ISA-Spezifikation ist offen nutzbar. Das heißt nicht, dass jede Implementierung automatisch Open Source ist. Viele CPU-Kerne sind proprietär, werden als IP lizenziert oder als fertige SoCs verkauft. Die Offenheit schafft aber einen größeren Spielraum: Sie können zwischen offenen Core-Designs, kommerziellen IP-Anbietern und Eigenentwicklungen wählen – und diese Entscheidung später leichter anpassen.

Diese Wahlfreiheit ist ein Hauptgrund, warum viele RISC-V als Marktveränderer sehen: Nicht zwingend, weil alle plötzlich alles offenlegen, sondern weil der ISA-Layer nicht mehr das Nadelöhr ist. Damit verschiebt sich Innovation stärker in Richtung Microarchitektur, Tooling, Beschleuniger und Plattformintegration – also dorthin, wo sich Produkte tatsächlich unterscheiden und Mehrwert entsteht.

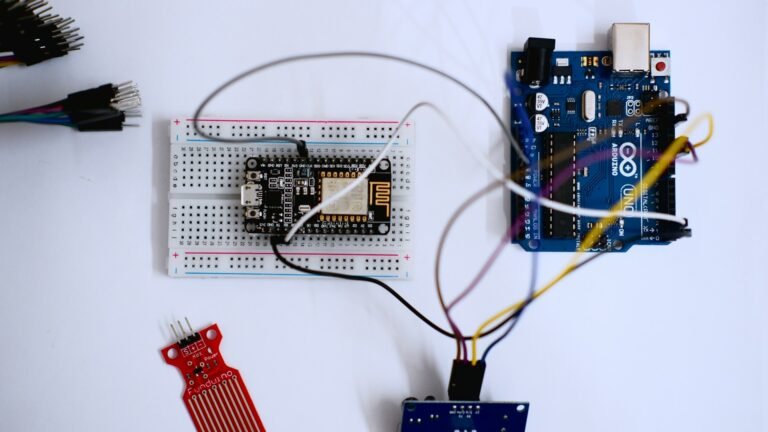

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.