Der SPI-Bus am PIC ist die erste Wahl, wenn Sie High-Speed-Datentransfer für typische Peripherie wie Displays, externe Flash-Bausteine oder SD-Karten benötigen. Im Gegensatz zu I²C ist SPI nicht als geteilter Zwei-Draht-Bus mit Pull-ups ausgelegt, sondern als taktsynchrones Punkt-zu-Mehrpunkt-Interface mit separater Chip-Select-Leitung pro Teilnehmer. Das macht SPI in vielen Designs schneller, deterministischer und einfacher zu debuggen – gleichzeitig verlangt es saubere Hardware und klare Software-Regeln: richtige Taktphase und -polarität (SPI-Mode), korrekte Pegel (3,3 V vs. 5 V), stabile Chip-Select-Steuerung und ein Layout, das auch bei mehreren MHz noch saubere Flanken liefert. Gerade bei SD-Karten und schnellen Displays treten typische Fehlerbilder auf, wenn man „einfach loslegt“: die SD-Karte bleibt in der Initialisierung hängen, das Display zeigt Artefakte, Daten werden sporadisch falsch gelesen oder der Bus funktioniert nur bei niedrigem Takt. In diesem Beitrag lernen Sie, wie Sie SPI am PIC strukturiert aufsetzen und optimieren – von den elektrischen Grundlagen über die MSSP/SSP-Konfiguration bis zu praxisbewährten Strategien für Display-Transfers und SD-Karten im SPI-Modus.

SPI-Grundprinzip: Leitungen, Rollen und warum es so schnell sein kann

SPI (Serial Peripheral Interface) ist ein synchrones serielles Protokoll, bei dem ein Master den Takt vorgibt und Daten gleichzeitig senden und empfangen kann (Full-Duplex). Klassisch bestehen die Verbindungen aus:

- SCK (SCLK): Taktleitung vom Master.

- MOSI: Daten vom Master zum Slave (auch SDI/SDO je nach Datenblattbezeichnung).

- MISO: Daten vom Slave zum Master.

- CS/SS: Chip-Select/Slave-Select (meist aktiv Low), pro Slave separat.

Der Geschwindigkeitsvorteil entsteht, weil SPI keine Adressierung im Protokoll benötigt und ohne Start/Stop-Overhead auskommt. Außerdem kann der Master den Takt relativ hoch wählen – begrenzt primär durch den PIC-Takt, das SPI-Modul, die Leitungsqualität und die Fähigkeiten des angeschlossenen Bausteins.

MSSP/SSP am PIC: Welche Hardware steckt dahinter?

Viele PIC-Controller nutzen ein MSSP- bzw. SSP-Modul (Master Synchronous Serial Port / Synchronous Serial Port), das SPI und häufig auch I²C unterstützt. Für die praktische Arbeit heißt das: Die gleichen Pins teilen sich oft mehrere Funktionen, und Sie müssen Pin-Multiplexing (z. B. PPS bei neueren PICs) korrekt konfigurieren. Einen kompakten Einstieg in Microchips SPI-/MSSP-Themenwelt bietet der Developer-Help-Bereich (je nach PIC-Familie) sowie die jeweiligen Datenblätter und Family Reference Manuals. Als allgemeiner Einstieg ist die Microchip-Übersicht zu MCC hilfreich, wenn Sie Konfiguration und Codegenerierung nutzen möchten: MPLAB Code Configurator (MCC) – Offizielle Übersicht.

Wichtig: Nicht jeder PIC unterstützt dieselben Komfortfunktionen. Manche Geräte bieten nur einfache SPI-Register (Byte-Transfer), andere haben erweiterte Features wie FIFO, Framing-Optionen oder DMA (bei größeren 16-/32-Bit-Familien). Trotzdem bleibt die Grundlogik identisch: Taktmodus korrekt wählen, Daten sauber takten, Chip-Select eindeutig steuern.

SPI-Mode verstehen: CPOL und CPHA entscheiden über „funktioniert“ oder „Müll“

Eine der häufigsten Ursachen für fehlerhafte SPI-Kommunikation ist ein falscher SPI-Mode. SPI kennt vier Standard-Modi, definiert durch:

- CPOL (Clock Polarity): Ruhezustand des Takts (SCK idle low oder idle high).

- CPHA (Clock Phase): Abtastzeitpunkt der Daten relativ zur Taktflanke (erste oder zweite Flanke).

Wenn CPOL/CPHA nicht zum Slave passt, lesen Sie Bits „zwischen den Flanken“, wodurch Daten verschoben oder komplett falsch interpretiert werden. Displays und SD-Karten sind hier besonders empfindlich, weil die erste Initialisierung bereits korrekt sein muss, bevor sinnvolle Antworten kommen. Prüfen Sie daher immer im Datenblatt des Zielbausteins, welcher Mode gefordert ist. Bei SD-Karten im SPI-Modus ist Mode 0 (CPOL=0, CPHA=0) in sehr vielen Implementierungen üblich, aber nicht als pauschale Regel zu verstehen – entscheidend ist die konkrete Spezifikation Ihres Stacks und Ihrer Hardware.

Chip-Select richtig behandeln: Warum „CS nebenbei toggeln“ Probleme macht

SPI ist ohne Chip-Select nicht robust. CS/SS signalisiert dem Slave, wann er Daten interpretieren soll und wann er MISO treiben darf. In Mehrslave-Setups ist CS zudem der zentrale Mechanismus, um Buskollisionen zu vermeiden.

- Pro Slave eine CS-Leitung: verhindert, dass mehrere Slaves gleichzeitig MISO aktiv treiben.

- CS sauber vor dem Transfer aktivieren: kurze Setup-Zeit einhalten, bevor die erste Taktflanke kommt.

- CS nach dem Transfer deaktivieren: ggf. Hold-Zeit einhalten, damit der Slave den Transfer abschließt.

- Kein „Flattern“: CS darf nicht durch Interrupts oder Nebenfunktionen unbeabsichtigt kurz deaktiviert werden.

Gerade bei SD-Karten ist CS-Handling kritisch: Viele Karten erwarten definierte Sequenzen, und ein unerwartetes CS-Togglen kann dazu führen, dass die Karte die Kommandoauswertung abbricht oder in einen unklaren Zustand gerät.

High-Speed beginnt in der Hardware: Pegel, Leitungslängen und Signalqualität

SPI wird schnell „zickig“, wenn die elektrische Auslegung nicht passt. Während I²C oft durch Pull-ups und Rise-Time-Limits begrenzt ist, sind es bei SPI vor allem Flanken, Überschwingen, Reflexionen und Pegelkompatibilität.

Pegelkompatibilität: 3,3 V ist bei SD-Karten praktisch Pflicht

SD-Karten arbeiten typischerweise mit 3,3-V-Logik. Wenn Ihr PIC mit 5 V läuft, brauchen Sie eine Pegelanpassung (Level Shifting) – zumindest für MOSI, SCK und CS. MISO von der SD-Karte (3,3 V) wird von vielen 5-V-PICs als High erkannt, aber darauf sollten Sie sich nur verlassen, wenn die Eingangspegel des PIC das sicher erlauben. Ein sauberer Level-Shifter oder geeignete Widerstands-/Pufferlösungen erhöhen die Robustheit deutlich.

Leitungslängen und Serienwiderstände

Bei einigen MHz können schon wenige Zentimeter Leiterbahn, Steckverbinder oder Flachbandkabel zu störenden Reflexionen führen. Ein häufig bewährter Praxisgriff sind kleine Serienwiderstände (z. B. 22–100 Ω) am Treiber (Master) in SCK und MOSI, um Flanken zu dämpfen und Überschwingen zu reduzieren. Das ist keine Universalregel, hilft aber in vielen realen Setups, insbesondere bei Displays auf Breakout-Boards oder SD-Kartenmodulen mit langen Leitungen.

SPI-Takt und Durchsatz: Realistisch planen statt „maximal drehen“

Für Displays und SD-Karten ist der Durchsatz entscheidend. Der theoretische Bitdurchsatz ergibt sich direkt aus der Taktfrequenz:

Bei 8 Bit pro Byte ergibt sich der Byte-Durchsatz:

In der Praxis ist der effektive Durchsatz kleiner, weil CS-Handling, Kommandobytes, Wartezyklen und Software-Overhead hinzukommen. Für Displays zählt außerdem, ob Sie viele kleine Transfers (ineffizient) oder große Burst-Transfers (effizient) senden. Bei SD-Karten hängt viel davon ab, ob Sie blockweise (typisch 512 Byte) arbeiten und ob Ihre Implementierung die Karte konsequent im Streaming hält.

SPI am PIC konfigurieren: Die typischen Stellschrauben

Unabhängig vom konkreten PIC-Modell tauchen bei SPI-Konfigurationen immer wieder dieselben Parameter auf:

- Master/Slave-Modus: In den meisten Fällen ist der PIC Master.

- SPI-Mode (CPOL/CPHA): passend zum Slave einstellen.

- Taktteiler: SCK aus Systemtakt ableiten (Fosc/4, /16, /64 o. ä., geräteabhängig).

- Datenrichtung/Pin-Mapping: MOSI/MISO korrekt und ggf. PPS richtig gesetzt.

- Sample-Point: manche Module erlauben zusätzlich die Wahl, wann das Eingangssignal abgetastet wird.

Wenn Sie MCC nutzen, können Sie viele dieser Optionen komfortabel setzen und erhalten initialen Treibercode. Dennoch sollten Sie die resultierenden Einstellungen gegen das Datenblatt des PIC und die Spezifikation des Slaves prüfen – gerade bei High-Speed lohnt sich diese Sorgfalt.

Displays über SPI: Schnell zeichnen, ohne die CPU zu blockieren

Viele TFT- oder OLED-Module (z. B. mit Controllern wie ILI9341, ST7735 oder SSD1306 in bestimmten Varianten) nutzen SPI, um Pixel- oder Befehlsdaten zu übertragen. Für gute Performance sind drei Prinzipien entscheidend:

- Große Transfers statt vieler kleiner: Pixel-Daten als Block senden (Burst), nicht Pixel für Pixel per Funktionsaufruf.

- DC/RS-Leitung sauber trennen: Viele Displays unterscheiden Command/Data über eine zusätzliche Leitung (D/C). Diese muss stabil zum Transfer passen.

- Chip-Select effizient nutzen: CS während eines kompletten Befehls- und Datensatzes aktiv lassen, statt pro Byte zu toggeln.

Fenster setzen: Der Schlüssel zu hoher Zeichenrate

Fast alle Grafikcontroller unterstützen „Address Window“-Kommandos: Sie definieren einen Rechteckbereich, in den danach fortlaufend Pixel geschrieben werden. Wenn Sie dieses Fenster nutzen, können Sie Pixeldaten streamen, ohne ständig neue Adressen zu senden. Das reduziert Overhead und erhöht den effektiven SPI-Durchsatz deutlich.

SPI und Interrupts: Vorsicht bei Timing und CS

Wenn während eines Display-Transfers Interrupts auftreten, kann das bei ungeschütztem CS-Handling zu Protokollfehlern führen. Eine robuste Lösung ist, kritische Transferabschnitte kurzzeitig zu schützen oder den SPI-Transfer als State Machine zu implementieren, die CS und D/C konsistent verwaltet. Auf leistungsfähigeren PICs kann DMA oder FIFO-Unterstützung die CPU entlasten – bei kleineren 8-Bit-PICs sind gut strukturierte Burst-Transfers der wichtigste Hebel.

SD-Karten im SPI-Modus: Initialisierung, Blockzugriff und typische Fehler

SD-Karten sind für viele Projekte attraktiv, weil sie große Speicherkapazitäten günstig verfügbar machen. Im SPI-Modus verhalten sie sich jedoch wie ein streng sequenzieller Protokollpartner: Sie erwarten definierte Kommandos, bestimmte Antwortformate und eine saubere Timingumgebung.

Initialisierung: langsamer Start, später schneller

Ein bewährtes Vorgehen ist, die SD-Karte mit niedriger SPI-Frequenz zu initialisieren und erst nach erfolgreichem Eintritt in den „Ready“-Zustand auf höhere Frequenzen umzuschalten. Das erhöht die Erfolgschance auf unterschiedlichsten Karten und reduziert Probleme durch noch nicht stabile Pegel oder zu lange Flanken. Der konkrete Ablauf hängt von Ihrer SD-SPI-Implementierung ab (CMD0, CMD8, ACMD41 usw.), aber die Grundidee bleibt: erst stabilisieren, dann beschleunigen.

Blockweise Transfers: 512 Byte als natürliche Einheit

SD-Karten arbeiten intern blockorientiert; im SPI-Modus werden Daten meist in 512-Byte-Blöcken übertragen. Für Performance und Stabilität sollten Sie:

- Immer ganze Blöcke lesen/schreiben: statt viele kleine Stücke.

- Timeouts einbauen: auf Response-Bytes und Data Tokens warten, aber nicht endlos.

- CRC/Checks (optional) verstehen: Im SPI-Modus ist CRC in vielen Szenarien optional, bei bestimmten Kommandos aber relevant.

Warum SD-Karten „zickig“ wirken

- Pegelproblem: 5-V-SPI ohne sauberen Level-Shifter führt zu sporadischen Fehlern.

- Zu schneller Takt: besonders beim Init oder bei langen Leitungen.

- CS nicht stabil: unerwartete CS-Flanken unterbrechen Kommandos.

- Stromversorgung: SD-Karten ziehen kurzzeitig höhere Ströme; mangelnde Entkopplung führt zu Resets oder Busfehlern.

Mehrere SPI-Teilnehmer: Displays, SD-Karte und Flash auf einem Bus

SPI eignet sich sehr gut, um mehrere Geräte zu verbinden, solange Sie die Regeln konsequent einhalten:

- Gemeinsame Leitungen: SCK, MOSI und MISO werden geteilt.

- Getrennte CS-Leitungen: jeder Slave hat seinen eigenen Chip-Select.

- MISO nur vom aktiven Slave: in der Regel tri-staten Slaves MISO, wenn CS inaktiv ist; prüfen Sie das im Datenblatt.

- Mode-Wechsel beachten: Wenn zwei Slaves unterschiedliche SPI-Modes brauchen, müssen Sie die PIC-SPI-Konfiguration beim Umschalten anpassen.

In der Praxis ist der Mode-Wechsel ein häufiger „versteckter“ Bug: Das Display läuft in Mode 0, ein anderes Gerät in Mode 3 – und plötzlich sind die Daten nur bei einem der Geräte korrekt. In solchen Systemen lohnt sich eine klar strukturierte „SPI-Bus-Layer“-Funktion, die vor jedem Zugriff Mode, Takt und CS konsistent setzt.

Fehlersuche mit System: Logic Analyzer schlägt Vermutung

SPI ist hervorragend messbar. Ein Logic Analyzer zeigt Ihnen sofort, ob Mode, CS und Datenbytes stimmen. Für effizientes Debugging:

- CS prüfen: ist CS während des Transfers stabil aktiv?

- Mode prüfen: passen Datenflanken und Sample-Punkte zum erwarteten Mode?

- Bytefolge prüfen: stimmen Kommandos/Antworten (z. B. SD-Responses, Display-IDs)?

- Timing prüfen: sind Pausen oder zusätzliche Clocks vorhanden, die der Slave nicht erwartet?

Wenn Sie zusätzlich ein Oszilloskop nutzen, sehen Sie Signalqualität: Überschwingen, langsame Flanken, Ringing. Gerade bei „läuft nur bei 1 MHz“-Problemen ist die Signalintegrität oft der eigentliche Grund.

Praxis-Checkliste: SPI-Bus am PIC für High-Speed stabil aufbauen

- SPI-Mode bestätigt: CPOL/CPHA aus dem Datenblatt des Slaves übernommen und getestet.

- Pegel kompatibel: insbesondere SD-Karte/Displays auf 3,3 V, Level-Shifting sauber umgesetzt.

- CS pro Slave: keine gemeinsamen CS-Leitungen, CS-Setup/Hold eingehalten.

- Layout geeignet: kurze Leitungen, saubere Masse, Entkopplung, optional Serienwiderstände.

- Takt realistisch gewählt: nach erfolgreicher Initialisierung hochdrehen, nicht umgekehrt.

- Burst-Transfers genutzt: große Datenblöcke statt viele kleine Transfers.

- Timeouts integriert: besonders bei SD-Karten und bei wartenden Responses.

- Bus-Layer vorhanden: zentrale SPI-Funktionen, die Mode/Takt/CS konsistent steuern.

- Messbar gemacht: Testkommandos, Log-Ausgaben und Logic-Analyzer-Checks eingeplant.

Weiterführende Outbound-Links: Verlässliche Einstiege und Referenzen

- MPLAB Code Configurator (MCC) – SPI schnell konfigurieren

- MPLAB X IDE – Entwicklungsumgebung für PIC-Projekte

- MPLAB XC8 Compiler – C-Toolchain für 8-bit PIC

- Microchip Developer Help: Peripherie-Übersicht (8-bit PIC)

- SD Association: Ressourcen und Spezifikationshinweise (SD-Karten)

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

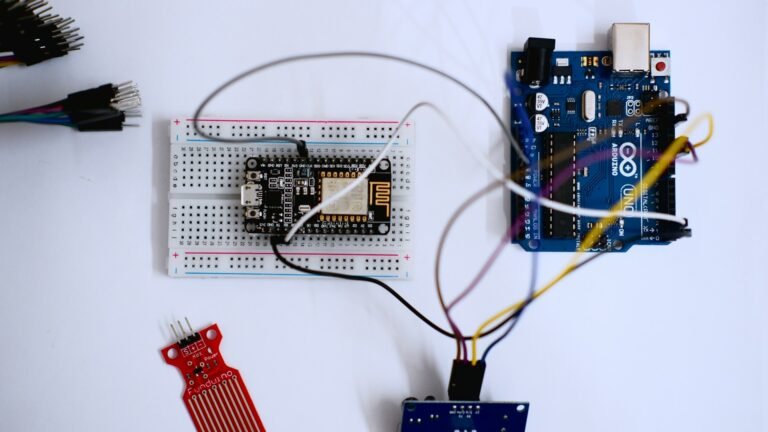

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.