STM32 Speicher-Management ist eine Kernkompetenz, wenn Embedded-Systeme zuverlässig, performant und wartbar sein sollen. In der Praxis entscheidet die Speicherarchitektur darüber, ob eine Applikation stabil startet, ob Echtzeitbedingungen eingehalten werden, wie schnell Daten verarbeitet werden können und wie robust Firmware-Updates im Feld funktionieren. STM32-Mikrocontroller kombinieren typischerweise internen Flash für Programmcode und persistente Daten, internes SRAM für Laufzeitdaten (Stacks, Heaps, Buffer) und – je nach Projekt – externes QSPI-Flash als kostengünstige Erweiterung für große Datenmengen, Assets oder zusätzliche Firmware-Slots. Die Herausforderungen sind dabei selten nur „zu wenig Speicher“, sondern meist die richtige Aufteilung: Welche Daten müssen schnell sein? Welche müssen dauerhaft sein? Wie vermeiden Sie Fragmentierung und Speicherlecks? Wie schützen Sie Flash vor unnötigem Verschleiß? Und wie nutzt man externes QSPI-Flash sinnvoll, ohne Bootzeit, Latenz oder Stromverbrauch unnötig zu verschlechtern? Dieser Artikel erklärt die wichtigsten Speicherarten und Konzepte, zeigt typische Layouts und Best Practices und vermittelt ein Vorgehen, mit dem Sie Speicherprobleme systematisch vermeiden statt später mühsam zu debuggen.

Speicherarten im STM32: Flash, SRAM und externe Erweiterungen

STM32-Systeme basieren in der Regel auf drei Säulen:

- Interner Flash: nichtflüchtig, enthält Programmcode, Konstanten und ggf. persistente Daten; begrenzte Schreibzyklen und seiten-/sektorbasierte Löschung.

- Interner SRAM: flüchtig, schnell, ideal für Variablen, Stacks, Heap, Echtzeitbuffer; verliert Inhalte beim Reset/Power-Off (außer in speziellen Backup-/Retention-SRAMs).

- Externes QSPI-Flash: nichtflüchtig, deutlich größer als interner Flash möglich, meist günstiger pro Bit; Zugriff langsamer und stärker latenzbehaftet, besonders bei zufälligen Reads.

Welche Speicheroptionen eine konkrete STM32-Serie bietet, hängt vom Modell ab. Als allgemeiner Einstieg in STM32-Serien und Tooling sind die Übersichten zu STM32 32-bit MCUs sowie zu STM32CubeMX nützlich, weil sie Produktfamilien und Konfigurationspfade zusammenfassen.

Memory Map verstehen: Warum Adressen und Busse wichtig sind

STM32-Mikrocontroller nutzen eine feste Memory Map: Bestimmte Adressbereiche sind für Flash, SRAM, Peripherie und externe Speicher reserviert. Je nach Serie kommen mehrere SRAM-Bänke, TCM-Speicher (bei Cortex-M7) oder spezielle Domains hinzu. Für das Speicher-Management bedeutet das:

- Geschwindigkeit hängt nicht nur vom Speicher ab: Auch Busanbindung, Arbitration und Caches beeinflussen Latenz und Durchsatz.

- DMA-Kompatibilität ist nicht überall gleich: Manche SRAM-Bereiche sind für bestimmte DMA-Controller besser geeignet als andere.

- Caches und MPU spielen eine Rolle: Besonders bei externem Flash oder DMA-Transfers müssen Cache-Attribute konsistent sein.

Gerade bei leistungsstärkeren STM32 (z. B. mit Cortex-M7) sollten Sie bewusst entscheiden, welche Daten in besonders schnellen internen Bereichen liegen und welche in „großen“, aber potenziell langsameren Speicherregionen. Hintergrund zur CPU-Architektur bietet die Übersicht zu Arm Cortex-M7.

Interner Flash: Code, Konfiguration und Grenzen durch Erase-Zyklen

Interner Flash ist der Standardort für Firmware. Er ist nichtflüchtig, relativ zuverlässig und wird vom Boot-ROM des STM32 direkt genutzt. Trotzdem hat Flash typische Eigenschaften, die das Design beeinflussen:

- Page/Sector Erase: Flash kann nur in größeren Blöcken gelöscht werden, nicht byteweise.

- Write-Granularität: Schreiben erfolgt in Wort-/Doppelwort-Schritten (serienabhängig), oft nur von 1 nach 0 ohne vorheriges Löschen.

- Begrenzte Endurance: Jede Flash-Page hat eine begrenzte Anzahl an Program/Erase-Zyklen.

- Read ist schnell, Write/Erase langsam: Erase kann Millisekunden dauern und blockiert je nach Architektur andere Aktivitäten.

Persistente Daten im internen Flash: Wear reduzieren

Konfigurationswerte, Zählerstände oder Kalibrierungen im Flash zu speichern ist verlockend, führt aber schnell zu Verschleiß, wenn zu häufig geschrieben wird. Eine robuste Strategie kombiniert:

- Write-Coalescing: Werte sammeln und nur selten schreiben (z. B. bei Zustandswechseln oder in festen Intervallen).

- Journal-/Log-Struktur: Statt immer dieselbe Adresse zu überschreiben, werden Einträge fortlaufend geschrieben, und beim Start wird der letzte gültige Eintrag gesucht.

- Wear-Leveling light: Mehrere Pages abwechselnd nutzen, um Zyklen zu verteilen.

- CRC/Versionierung: Jede Struktur mit Prüfsumme und Versionsfeld absichern, um Datenintegrität zu garantieren.

Endurance grob abschätzen

Eine einfache Abschätzung hilft, ob ein Flash-basiertes Speicherkonzept realistisch ist. Wenn eine Page

Diese Rechnung ist bewusst vereinfacht, macht aber sichtbar: Häufiges Schreiben (z. B. jede Sekunde) ist im internen Flash meist keine gute Idee. In solchen Fällen sind FRAM, externes Flash mit Wear-Leveling oder ein Dateisystem auf SD-Karte oft die bessere Wahl.

SRAM: Laufzeitdaten, Stack/Heap und Echtzeitpuffer

SRAM ist das Arbeitspferd Ihrer Applikation. Hier liegen Variablen, Stacks, Heaps und temporäre Buffer. Typische Ursachen für Instabilität sind nicht „SRAM zu klein“, sondern falsche Nutzung:

- Stack overflow: besonders bei tiefen Call-Stacks, großen lokalen Arrays oder RTOS-Tasks mit zu kleinen Stacks.

- Heap fragmentation: häufiges malloc/free mit wechselnden Blockgrößen führt zu Fragmentierung.

- Unbounded buffers: dynamisch wachsende Strukturen ohne harte Limits.

Stack- und Heap-Strategien für robuste Systeme

- Statische Allokation bevorzugen: Besonders für Echtzeitkomponenten sind statische Buffer berechenbarer.

- Pool-Allocator einsetzen: Feste Blockgrößen verhindern Fragmentierung und sind deterministischer.

- Große lokale Arrays vermeiden: Stattdessen statisch oder global allokieren, oder in speziellen Buffer-Sektionen platzieren.

- Stack High-Water-Mark messen: In Tests gezielt auslasten und Stack-Reserven realistisch dimensionieren.

Linker-Skript und Sektionen: Speicherlayout bewusst gestalten

Das STM32 Speicher-Management wird in der Praxis stark durch das Linker-Skript bestimmt. Dort definieren Sie, welche Sektionen (z. B. .text, .rodata, .data, .bss, .heap, .stack) in welchen Speicherbereichen liegen. Ein sauberes Layout verfolgt klare Ziele:

- Code in Flash: .text und meist .rodata.

- Initialisierte Daten: .data liegt im SRAM, wird aber beim Start aus Flash kopiert.

- Null-initialisierte Daten: .bss im SRAM, wird beim Start genullt.

- Hot-Daten separat: zeitkritische Buffer in den schnellsten SRAM-Bereich oder TCM (wenn vorhanden).

Startup-Kosten verstehen: Kopieren und Nullsetzen

Der Reset-Handler kopiert .data aus Flash ins SRAM und löscht .bss. Große .data/.bss-Sektionen erhöhen Bootzeit und Energiebedarf beim Start. Wenn Sie große Tabellen oder Assets im SRAM halten, überlegen Sie, ob diese wirklich initialisiert sein müssen oder ob sie als read-only im Flash verbleiben können.

Externes QSPI-Flash: Kapazität gewinnen, aber mit Systemdenken

Externes QSPI-Flash (häufig über QUADSPI oder OCTOSPI/OSPI angebunden, je nach STM32-Serie) ist eine sehr gängige Erweiterung: Mehr Speicher für Bilder, Audio, Modelle, Logdaten oder zusätzliche Firmware-Slots. Die wichtigsten Eigenschaften:

- Nichtflüchtig und groß: typischerweise mehrere MByte bis deutlich darüber, abhängig vom Baustein.

- Serielles Interface: weniger Pins als paralleles Speicherinterface, aber höhere Latenz als internes SRAM.

- Memory-Mapped Mode möglich: Viele STM32 können QSPI-Flash so abbilden, dass es wie normaler Speicher gelesen wird (XIP: Execute in Place für Code ist je nach Serie/Toolchain realistisch, aber sorgfältig zu prüfen).

- Erase/Write wie Flash: sektorbasiert, Endurance beachten, Writes sind langsam und müssen geplant werden.

Wann QSPI-Flash ideal ist

- Große read-only Assets: Fonts, Bilder, UI-Resources, Lookup-Tabellen.

- Firmware-Update-Slots: zweite Firmware für A/B-Updates, Rollback und sichere Feldupdates.

- Logging mit Journaling: große Logbereiche, wenn SD-Karte nicht möglich ist (mit Wear-Leveling-Konzept).

- ML-Modelle und Parameter: Modelle/Weights, die nicht ins interne Flash passen.

Execute-in-Place und Memory-Mapped Reads: Performance realistisch bewerten

Memory-Mapped QSPI vermittelt den Eindruck, als wäre externes Flash „fast wie interner Flash“. In der Praxis sind Latenzen und Burst-Verhalten entscheidend. Viele Systeme profitieren, wenn häufig genutzter Code oder Daten in internes Flash/SRAM gelegt werden, während selten genutzte oder große read-only Daten im QSPI bleiben.

Eine einfache Durchsatzabschätzung (idealisiert) bei seriellen Interfaces lautet:

Dabei ist

Caches und Prefetch: Der Unterschied zwischen „geht“ und „läuft schnell“

Wenn der MCU-Kern Caches nutzt (z. B. Cortex-M7), können wiederholte Reads aus Memory-Mapped QSPI deutlich schneller werden, weil Cache-Hits Latenzen maskieren. Gleichzeitig müssen Sie sauber planen:

- Code im QSPI nur, wenn stabil: XIP erhöht Komplexität im Boot und bei Fehlerfällen.

- DMA-Reads aus QSPI beachten: DMA und Caches können sich gegenseitig beeinflussen; Buffer-Attribute sind wichtig.

- Dummy-Cycles tunen: Zu wenige Dummy-Cycles führen zu Bitfehlern, zu viele kosten Performance.

Firmware-Updates und Boot-Design: Interner Flash plus QSPI als Sicherheitsnetz

Ein professionelles Speicher-Management umfasst oft auch ein Update-Konzept. Externes QSPI-Flash eignet sich hervorragend, um eine zweite Firmware-Version zu speichern, bevor Sie den internen Flash überschreiben. Damit lassen sich A/B-Updates und Rollback realisieren.

- Bootloader im internen Flash: minimal, robust, selten geändert.

- Applikation A im internen Flash: aktuell laufende Version.

- Applikation B im QSPI: neue Version, erst nach Validierung aktiviert.

- Integritätsprüfung: Hash/CRC und Versionsverwaltung, damit fehlerhafte Images nicht gebootet werden.

Speicherlayout für Updates: Klar getrennte Regionen

Planen Sie feste Partitionen: Bootloader, App, Konfigurationsbereich, eventuell Crash-Logs. Je klarer die Grenzen, desto weniger Risiko, versehentlich kritische Bereiche zu überschreiben. Vermeiden Sie „dynamische“ Speicherplätze für Firmware, wenn Feldupdates zuverlässig funktionieren sollen.

Datenspeicherung: Konfiguration, Logs und Dateisysteme sinnvoll trennen

Ein häufiger Fehler ist, Konfiguration, Logs und Firmware im selben Flashbereich zu vermischen. Besser ist eine klare Trennung nach Zugriffsmustern:

- Konfiguration: seltene Writes, hohe Integrität; Journal- oder Key-Value-Ansatz mit CRC.

- Logs: viele Writes, große Datenmengen; ringförmig, segmentiert, mit Commit-Markern.

- Firmware: große, seltene Writes; strikt partitioniert, mit Validierung.

Checksummen und Commit-Modelle

Gerade bei Stromausfall muss klar erkennbar sein, ob ein Datensatz vollständig geschrieben wurde. Ein bewährtes Muster ist: zuerst Payload schreiben, dann Header mit CRC und „valid“-Flag am Ende. Alternativ arbeiten Sie mit zwei Kopien und einem Generation-Counter. Ziel ist immer: beim Boot eindeutig und ohne aufwendiges Scannen zu entscheiden, welche Daten gültig sind.

RAM-Optimierung in der Praxis: Große Buffer, Alignment und DMA

Viele STM32-Anwendungen sind datengetrieben: ADC-Buffer, Kommunikationspuffer, Display-Framebuffers, Audio-Buffers. Hier hilft konsequente Planung:

- Alignment: Buffer auf Wort-/Cache-Line-Grenzen ausrichten, um DMA und Cache effizient zu nutzen.

- Double Buffering: während Buffer A verarbeitet wird, füllt DMA Buffer B (oder umgekehrt).

- Zero-Copy, wo sinnvoll: unnötige Kopien vermeiden, aber nicht auf Kosten von Datenkonsistenz.

- Heap klein halten: große Datenstrukturen lieber statisch oder in Pools.

Fehlersuche: Typische Symptome von schlechtem Speicher-Management

- Random Crashes nach Minuten/Stunden: oft Stack overflow, Heap fragmentation oder Use-after-free.

- Boot hängt sporadisch: fehlerhafte .data/.bss-Initialisierung, QSPI nicht früh genug initialisiert, falsche Clock/Dummy-Cycles.

- Logs/Config manchmal korrupt: fehlende CRC/Commit-Logik, Stromausfall während Write, Cache/DMA-Kohärenzfehler.

- Performance „unerklärlich“ schlecht: Hot-Daten im falschen SRAM-Bereich, Cache-Misses, zu viele Flash-Erases, unpassende QSPI-Modi.

Messbarkeit schaffen: Map-Datei und Speicherstatistiken nutzen

Nutzen Sie die Linker-Map-Datei, um zu sehen, welche Sektionen wie viel Speicher belegen. Ergänzen Sie Laufzeitmetriken: Stack-High-Water-Mark pro Task, Heap-Usage, Anzahl von Allocations, Peak-Buffergrößen. Nur so wird Speicher-Optimierung systematisch statt „Trial and Error“.

Best Practices: Ein solides STM32 Speicher-Management in 10 Punkten

- Speicher nach Zugriffsmuster planen: hot vs. cold, read-only vs. write-heavy.

- Linker-Skript bewusst gestalten: klare Regionen und Sektionen, keine „Zufallsverteilung“.

- Flash-Writes minimieren: bündeln, journaling, wear-leveling light, CRC.

- Konfigurationsdaten robust speichern: Version, CRC, Commit-Flag, ggf. doppelte Kopie.

- Heap vermeiden oder kontrollieren: Pools, statische Allokation, klare Limits.

- Stack realistisch dimensionieren: messen statt raten, lokale Arrays vermeiden.

- QSPI nur dort einsetzen, wo es passt: große Assets, Update-Slots, seltene Daten; Hot-Code eher intern.

- Cache/MPU/DMA sauber definieren: besonders bei Cortex-M7 und externen Speicherzugriffen.

- Fehlerfälle designen: Stromausfall während Write, Update-Abbruch, fehlender QSPI-Baustein.

- Dokumentation pro Projekt: Memory Map, Partitionen, Update-Flow und Datenformate schriftlich festhalten.

Für die praktische Umsetzung im Projektalltag sind die Konfigurationswerkzeuge von ST wie STM32CubeMX sowie die passenden Reference Manuals und Datenblätter Ihrer STM32-Serie die wichtigste Grundlage, weil dort Memory Map, Flash-Eigenschaften und QSPI/OSPI-Modi verbindlich beschrieben sind. Mit einem klaren Layout, robusten Persistenzmustern und einer bewussten Trennung zwischen internem Flash, SRAM und externem QSPI-Flash wird STM32 Speicher-Management zu einem planbaren Engineering-Thema statt zu einer späten Krisenursache.

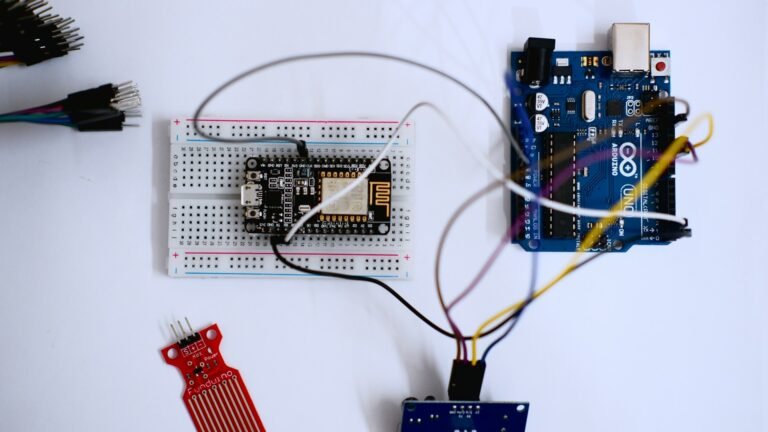

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.