Das STM32 Taktsystem (RCC) ist die Schaltzentrale für nahezu alles, was in einem STM32-Mikrocontroller mit Timing, Performance und Stabilität zu tun hat. Wer „einfach nur“ die CPU schnell taktet, erlebt in der Praxis schnell Überraschungen: USB enumeriert nicht zuverlässig, UART-Baudraten driften, Timer-Frequenzen passen nicht, der ADC sampelt mit Jitter oder das System wird instabil, sobald Temperatur oder Versorgung schwanken. Der Grund ist simpel: Der perfekte Takt ist nicht nur eine Zahl in MHz, sondern ein abgestimmtes Gesamtsystem aus Taktquellen, PLLs, Busprescalern und Peripherie-Kerntakten. Insbesondere USB ist anspruchsvoll, weil es sehr präzise Taktraten erwartet (typisch 48 MHz für Full-Speed-USB). Gleichzeitig wollen Sie die CPU so hoch takten, wie es Ihre Anwendung erfordert – aber ohne unnötigen Energieverbrauch oder Timing-Probleme. Dieser Artikel erklärt das RCC-Konzept verständlich, zeigt typische Clock-Tree-Setups für USB und CPU und vermittelt ein Vorgehen, mit dem Sie systematisch den „perfekten“ Takt finden: reproduzierbar, wartbar und robust für reale Produkte.

RCC und Clock Tree: Was steckt hinter dem Taktsystem?

RCC steht für „Reset and Clock Control“. In STM32-Mikrocontrollern steuert RCC, welche Taktquelle aktiv ist, wie daraus System- und Peripherie-Takte entstehen und welche Module überhaupt getaktet werden. Der Clock Tree ist dabei die grafische Darstellung der Signalwege: Von einer Quelle (z. B. HSE-Quarz) über eine PLL und Prescaler bis zu CPU, AHB/APB-Bussen und Peripherie-Kerntakten.

- Taktquellen: interne RC-Oszillatoren, externe Quarze/Clock-Eingänge, Low-Speed-Quellen für RTC.

- PLLs: vervielfachen und teilen Frequenzen, um Zielwerte für CPU und Peripherie zu erzeugen.

- Busprescaler: teilen den Systemtakt für AHB/APB, beeinflussen Timer- und Peripherietakte.

- Clock Gating: Abschalten von Peripherie-Clocks zur Energieeinsparung.

Für die praktische Konfiguration ist STM32CubeMX sehr verbreitet, weil dort der Clock Tree visuell aufgebaut und plausibilisiert werden kann. Für allgemeine STM32-Übersichten ist die ST-Seite zu STM32 32-bit MCUs ein guter Einstieg.

Taktquellen verstehen: HSI, HSE, LSI, LSE und was sie bedeuten

Bevor Sie PLLs einstellen, sollten Sie die Eigenschaften der Taktquellen kennen. Die Namen können je nach Serie leicht variieren, das Prinzip ist jedoch ähnlich:

- HSI (High-Speed Internal): interner RC-Oszillator, schnell verfügbar, kostengünstig (kein Quarz), aber typischerweise ungenauer als ein Quarz.

- HSE (High-Speed External): externer Quarz oder externer Clock-Eingang, sehr stabil und präzise; oft Grundlage für zuverlässiges USB.

- LSI (Low-Speed Internal): interner Low-Speed-Oszillator, meist für Watchdog/RTC-ähnliche Funktionen, aber driftanfälliger.

- LSE (Low-Speed External, 32,768 kHz): Quarz für RTC, hohe Genauigkeit bei niedrigem Verbrauch.

Wenn USB eine Rolle spielt, ist Präzision entscheidend. Viele Designs nutzen HSE als Basis, weil ein Quarz die Frequenzstabilität verbessert und Temperaturdrift reduziert. Je nach STM32-Serie gibt es auch interne Mechanismen zur USB-Taktgenerierung und Korrektur, jedoch ist ein sauberer, stabiler Taktpfad der robusteste Weg.

Warum USB so taktsensibel ist: 48 MHz als harte Anforderung

USB Full Speed (FS) erwartet typischerweise eine sehr genaue 48-MHz-Taktbasis für die USB-Peripherie. Auch wenn nicht jede Serie den 48-MHz-Takt exakt gleich erzeugt, gilt als Faustregel: Der USB-Kerntakt muss stabil und präzise sein, sonst treten Symptome auf wie:

- Enumeration schlägt sporadisch fehl (Gerät wird nicht erkannt oder bricht ab).

- Verbindungsabbrüche unter Last oder bei bestimmten Hosts/Hubs.

- Timing-Probleme bei isochronen Transfers (Audio) oder hohen Datenraten.

Aus RCC-Sicht bedeutet das: Sie brauchen entweder eine PLL-Konfiguration, die eine saubere 48-MHz-Ableitung liefert, oder eine dedizierte 48-MHz-Quelle (serienabhängig). Die wichtigste Fähigkeit ist, aus Ihrer Referenzquelle (HSE oder HSI) eine exakt passende Frequenz zu synthetisieren.

PLL-Grundlagen: Frequenzen sauber berechnen

Eine PLL (Phase-Locked Loop) erzeugt aus einer Eingangsfrequenz fin eine neue Frequenz fout durch Multiplikation und Division. Die konkreten Parameter heißen je nach STM32-Serie unterschiedlich (z. B. M/N/P/Q/R oder ähnliche). Das generische Prinzip lässt sich dennoch gut darstellen:

Aus der VCO-Frequenz werden dann verschiedene Ausgänge abgeleitet, etwa für CPU (SYSCLK) und für USB (48 MHz):

Die Kunst ist, M/N/P/Q (bzw. die entsprechenden Parameter Ihrer Serie) so zu wählen, dass fUSB exakt 48 MHz ergibt und fSYS zur gewünschten CPU-Frequenz passt – ohne VCO-Grenzen, Flash-Waitstates oder Buslimits zu verletzen.

Der perfekte Takt: Zielkonflikte zwischen CPU-Performance und USB-Stabilität

In der Praxis konkurrieren mehrere Ziele:

- CPU schnell genug: um Rechenlast, Interrupts, Protokolle oder DSP zu schaffen.

- USB exakt genug: damit Enumeration und Datenübertragung zuverlässig laufen.

- Bus- und Peripheriegrenzen: AHB/APB dürfen bestimmte Frequenzen nicht überschreiten.

- Energieverbrauch: höhere Takte erhöhen meist den Verbrauch, besonders in aktiven Phasen.

„Perfekt“ ist daher nicht immer „maximal“. Häufig ist ein etwas niedrigerer CPU-Takt die bessere Wahl, wenn er eine saubere USB-Taktableitung ohne exotische PLL-Parameter ermöglicht und gleichzeitig Wärme, EMV und Stromaufnahme reduziert.

Busprescaler und Timer-Falle: Warum APB-Einstellungen überraschende Effekte haben

Ein zentraler Punkt im STM32 Taktsystem (RCC) sind die Busprescaler. Üblicherweise gibt es AHB (für Core/Memory/High-Speed-Bus) und APB-Busse (APB1/APB2, teils weitere Domains). Peripherie hängt an diesen Bussen, und deren Takt bestimmt Baudraten, Timer-Frequenzen und Interrupt-Last.

- AHB: beeinflusst CPU-nahe Komponenten und viele Peripherien.

- APB: beeinflusst Timer, UART, I2C, SPI und weitere Module.

Timer-Clock-Multiplikation: Der Klassiker

In vielen STM32-Familien gilt: Wenn ein APB-Prescaler größer als 1 ist, takten Timer auf diesem APB häufig mit dem doppelten APB-Takt. Das ist nützlich, aber tückisch: Wer nur den APB-Takt betrachtet, berechnet PWM oder Zeitbasen falsch. Deshalb sollten Sie im Clock Tree immer den tatsächlichen Timer-Kerntakt prüfen und Ihre Formeln darauf beziehen.

Flash-Latenz und Spannungsbereich: Ohne Waitstates wird es instabil

Ein STM32 kann nur dann stabil schnell laufen, wenn Flash-Waitstates und Versorgungseinstellungen passen. Höhere CPU-Frequenzen benötigen oft mehr Waitstates, und manche Serien verlangen bestimmte Power-Scaling-Einstellungen, bevor hohe SYSCLK-Werte zulässig sind. Typische Symptome bei falscher Einstellung:

- Random HardFaults oder unerklärliche Abstürze bei höherem Takt.

- Instabilität nur bei Temperaturänderung oder bei bestimmten Compiler-Optimierungen.

- USB-Probleme als Nebeneffekt, weil das System nicht deterministisch läuft.

Der praktische Rat: Stellen Sie zuerst den Spannungs-/Power-Scale korrekt ein, dann Flash-Waitstates, und erst danach erhöhen Sie den Systemtakt. STM32CubeMX zeigt diese Abhängigkeiten oft an, ersetzt aber nicht den Blick ins Datenblatt Ihrer konkreten MCU.

Typische Clock-Tree-Strategien für USB + CPU

Je nach STM32-Serie existieren mehrere robuste Strategien. Entscheidend ist, welche Referenzquelle Sie verwenden und wie flexibel die PLL-Ausgänge sind.

- HSE (Quarz) als Basis: sehr häufig für USB-Projekte, weil die Referenz stabil ist.

- HSI als Basis: möglich, wenn die interne Genauigkeit ausreicht oder die Serie USB-taugliche Taktkorrektur bietet; oft günstiger in BOM.

- Dedizierte 48-MHz-Domain: manche Serien haben spezielle PLL-Ausgänge oder 48-MHz-Generatoren für USB/SDMMC/RNG.

Warum 8 MHz und 16 MHz Quarze so beliebt sind

Viele Boards verwenden 8 MHz oder 16 MHz HSE, weil diese Frequenzen in zahlreichen STM32-PLL-Konfigurationen gut zu ganzzahligen Teilern passen. Dadurch wird es einfacher, sowohl 48 MHz für USB als auch einen hohen SYSCLK für die CPU zu erzeugen, ohne komplizierte Brüche oder Randbereiche der PLL zu nutzen.

USB und CPU gleichzeitig optimieren: Ein systematisches Vorgehen

Um den perfekten Takt für USB und CPU zu finden, bewährt sich ein klarer Ablauf:

- Zielwerte festlegen: gewünschter CPU-Takt (SYSCLK), benötigte Peripherie-Takte (USB 48 MHz, ggf. SDMMC, ADC, Audio).

- Referenzquelle wählen: HSE, HSI oder externer Clock; Entscheidung nach Kosten, Genauigkeit, Startup-Zeit.

- PLL so wählen, dass USB exakt 48 MHz erhält: USB zuerst „hart“ absichern, danach CPU optimieren.

- Busprescaler dimensionieren: APB-Frequenzen im zulässigen Bereich, Timer-Effekte berücksichtigen.

- Flash-Waitstates und Power-Scaling einstellen: Stabilität vor Feintuning.

- Validieren: USB Enumeration, Datentransfer unter Last, Temperaturtest, Brownout-Szenarien.

RCC in CubeMX und Code: Was Sie unbedingt kontrollieren sollten

STM32CubeMX ist hilfreich, weil es Abhängigkeiten sichtbar macht. Trotzdem sollten Sie einige Punkte bewusst prüfen, statt sich blind auf Auto-Settings zu verlassen:

- USB-Kerntakt: wirklich 48 MHz und aus der richtigen Quelle abgeleitet.

- PLL-VCO-Bereich: nicht am Rand; konservative Werte sind oft stabiler.

- AHB/APB-Frequenzen: innerhalb Spezifikation; Timer-Kerntakte korrekt.

- Clock Security/Failover: wenn HSE ausfällt, was passiert? (serienabhängig)

- Startup-Reihenfolge: Oszillator an, stabil warten, PLL locken, dann Umschalten auf SYSCLK.

Clock-Ausfall und Robustheit

In industriellen Umgebungen können Quarze oder externe Clock-Quellen durch Störungen, Lötprobleme oder extreme Bedingungen ausfallen. Wenn Ihre Anwendung kritisch ist, lohnt es sich, über Mechanismen zur Clock-Überwachung und ein definiertes Fallback nachzudenken. Das ist kein „Standard in jedem Projekt“, aber bei robusten Feldgeräten oft ein echter Qualitätsfaktor.

Präzision vs. Kosten: Wann ein Quarz wirklich notwendig ist

Ein Quarz erhöht BOM und benötigt Layout-Sorgfalt, liefert aber stabile Frequenzen. Bei USB ist das oft der sicherste Weg. Dennoch gibt es Anwendungsfälle, in denen ein interner Oszillator ausreichen kann, etwa bei Kosten- oder Platzdruck und wenn die MCU-Serie geeignete Kalibriermechanismen bietet oder USB nicht permanent aktiv ist. Die Entscheidung sollte technisch begründet sein:

- USB als Kernfunktion: meist HSE empfohlen.

- USB selten genutzt: unter Umständen reicht HSI, wenn Validierung besteht.

- Hohe Temperaturspanne: Quarz ist meist robuster als RC ohne Kompensation.

Peripherie-Kerntakte: USB ist nicht allein

Viele Projekte haben neben USB weitere peripheriegetriebene Taktanfordungen: SDMMC, I2S/SAI für Audio, ADC mit bestimmten Samplingraten, Ethernet-Referenzen oder präzise Timer. Das RCC-Design sollte daher nicht „USB vs. CPU“ isoliert betrachten, sondern den gesamten Taktbedarf sammeln. Ein praktischer Ansatz ist eine kleine Anforderungsliste:

- USB: 48 MHz präzise.

- CPU: so hoch wie nötig, so niedrig wie sinnvoll.

- Timer/PWM: Frequenzen und Auflösung, ggf. Center-Aligned-Modi.

- Kommunikation: UART/SPI/I2C-Baudraten, Toleranzen, Oversampling.

Beispiel: Timer-Frequenz aus RCC ableiten

Wenn ein Timer mit einem Kerntakt fTIM läuft und Prescaler PSC sowie Auto-Reload ARR nutzt, ist die Update-Frequenz näherungsweise:

Diese Formel zeigt, warum RCC und Prescaler zusammen gedacht werden müssen: Eine Änderung im Clock Tree verändert unmittelbar PWM, Zeitbasen und Trigger-Frequenzen.

Fehlersymptome beim RCC: Was typische Probleme wirklich bedeuten

Wenn das Taktsystem nicht sauber ist, äußert sich das häufig mit klaren Mustern:

- USB enumeriert nicht: 48 MHz nicht korrekt, falsche Quelle, PLL nicht stabil, zu hohe Jitter/Drift.

- UART „komisch“: Baudrate passt nicht, Oversampling/Clock falsch, APB-Clock geändert.

- Timer/PWM daneben: APB-Prescaler und Timer-Clock-Multiplikation nicht berücksichtigt.

- Random Faults bei hohem Takt: Flash-Waitstates/Power-Scaling nicht passend, VCO am Rand.

- Probleme nur nach Stop/Wakeup: Clock-Reinitialisierung nach Low-Power-Modi unvollständig.

Debugging-Tipp: Clock Tree als „Single Source of Truth“

Statt an fünf Stellen im Code zu raten, sollten Sie den Clock Tree als Referenz definieren: Welche Frequenzen liegen wo an? Was ist SYSCLK, HCLK, PCLK1/2 und der USB-Kerntakt? In CubeMX lässt sich das visuell prüfen; im Code sollten Sie bei Bedarf die effektiven Frequenzen aus den RCC-Statuswerten ableiten oder mit Debug-Ausgaben verifizieren (im Thread-Kontext, nicht in kritischen ISRs).

Best Practices: So wird der RCC-Entwurf wartbar und robust

- USB zuerst absichern: 48 MHz als harte Anforderung, dann CPU-Frequenz wählen.

- Konservative PLL-Settings: nicht am VCO-Limit; Stabilität schlägt „letzte MHz“.

- Prescaler bewusst setzen: APB-Limits und Timer-Effekte dokumentieren.

- Flash/Power-Scaling korrekt: Waitstates und Spannungsbereich vor Taktsteigerung.

- Low-Power-Resume planen: nach Stop/Standby den Clock Tree sauber wiederherstellen.

- Dokumentation im Projekt: Zielwerte, Quellen, PLL-Parameter, Busfrequenzen und USB-Pfad festhalten.

- Validierung unter Last: USB-Transfers, CPU-Lastspitzen, Temperaturtests und Versorgungsschwankungen.

Wer das STM32 Taktsystem (RCC) als ganzheitlichen Clock-Tree-Entwurf betrachtet, findet zuverlässig den perfekten Takt für USB und CPU: USB bekommt eine stabile, exakte 48-MHz-Basis, die CPU erreicht die benötigte Performance, und Bus- sowie Peripherie-Takte bleiben im spezifizierten Bereich. Für die praktische Umsetzung sind STM32CubeMX als Konfigurationshilfe sowie die MCU-spezifischen Datenblätter und Reference Manuals die wichtigsten Quellen, weil dort Grenzwerte, PLL-Parameter und Taktpfade verbindlich dokumentiert sind. Mit einem strukturierten Vorgehen, klaren Zielwerten und konsequenter Validierung wird RCC von einer Fehlerquelle zu einem stabilen Fundament für performante und USB-robuste STM32-Systeme.

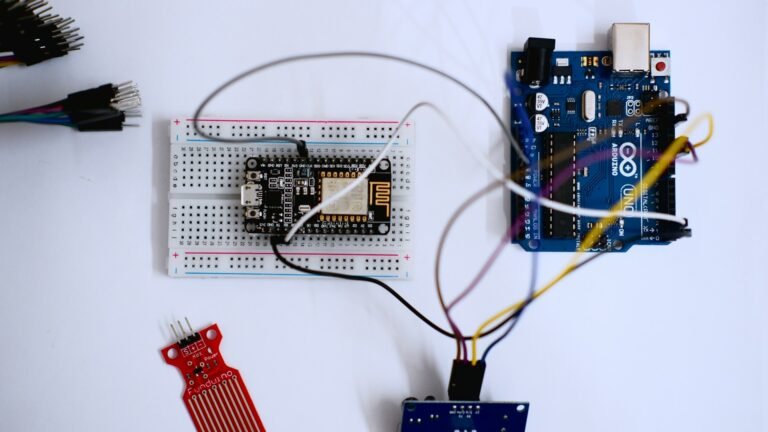

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.