Der Watchdog-Timer (WDT) ist eine der wirksamsten und zugleich am häufigsten missverstandenen Schutzfunktionen, wenn es darum geht, industrielle PIC-Steuerungen abzusichern. In rauen Umgebungen – mit EMV-Störungen, Spannungseinbrüchen, langen Leitungen, induktiven Lasten oder sporadischen Kommunikationsfehlern – ist ein „Hänger“ der Firmware kein theoretisches Risiko, sondern eine realistische Betriebssituation. Ohne Gegenmaßnahmen bleibt ein System dann im schlimmsten Fall in einem undefinierten Zustand stehen: Ausgänge bleiben gesetzt, Sicherheitsfunktionen reagieren nicht mehr, Messwerte frieren ein oder Feldbus-Teilnehmer blockieren. Genau hier greift der WDT: Er überwacht, ob die Software regelmäßig in einen „gesunden“ Ablauf zurückkehrt. Bleibt dieser Nachweis aus, löst der Watchdog einen Reset aus und bringt die Steuerung in einen definierten Startzustand zurück. Damit wird aus einem unkontrollierten Stillstand ein kontrolliertes Wiederanlaufen. Entscheidend ist jedoch, wie der Watchdog konfiguriert und in die Systemarchitektur eingebettet wird. Ein falsch integrierter WDT kann Fehler verschleiern, durch unpassende Zeitfenster unnötige Resets verursachen oder – noch schlimmer – durch „blindes Füttern“ wirkungslos werden. In diesem Beitrag erfahren Sie, wie Sie den Watchdog-Timer in PIC-Projekten so einsetzen, dass er wirklich Schutz bietet: von der Auswahl der WDT-Strategie über die richtige Timeout-Dimensionierung bis zur Diagnose von Reset-Ursachen und zur Kombination mit Fail-Safe-Hardware.

Was der Watchdog wirklich leistet – und was nicht

Ein Watchdog ist kein „Fehlerverhinderer“, sondern ein Fehlerbegrenzer. Er verhindert nicht, dass Bugs, Störungen oder unerwartete Zustände auftreten, aber er sorgt dafür, dass das System nicht dauerhaft in einem defekten Zustand verharrt. Der WDT beantwortet im Kern eine einzige Frage: „Kommt die Software regelmäßig an einem Punkt vorbei, der beweist, dass sie noch lebt?“

- WDT kann: Firmware-Hänger erkennen (z. B. Deadlocks, Endlosschleifen, blockierende Treiber), sporadische Störzustände entschärfen, definierte Neustarts erzwingen.

- WDT kann nicht: Datenkorruption automatisch beheben, logische Fehlentscheidungen verhindern, Hardwaredefekte reparieren oder Safety-Normen allein erfüllen.

- WDT ist besonders stark: wenn er mit Reset-Diagnose, sicheren Ausgangszuständen und robustem Start-up kombiniert wird.

Microchip beschreibt den Watchdog-Reset und typische Reset-Mechanismen für PIC-Familien in der eigenen Entwicklerdokumentation; als praxisnaher Einstieg eignet sich beispielsweise die Übersicht zu Watchdog-Resets: Microchip Developer Help: Watchdog Timer Reset bei 8-bit PIC.

Typische Fehlerbilder in industriellen PIC-Steuerungen, die der WDT abfängt

In industriellen Steuerungen entstehen Hänger selten durch „klassische“ Programmierfehler allein, sondern oft durch Grenzfälle aus Timing, Störungen und Peripherie-Zuständen. Der Watchdog ist eine Art Sicherheitsnetz für genau diese „nicht reproduzierbaren“ Situationen.

- Kommunikations-Deadlock: UART/RS485 wartet endlos auf ein Byte, Bus bleibt blockiert, Protokoll-State-Machine hängt.

- Peripherie bleibt in Fehlerzustand: I²C-Bus stuck low, SPI-Transfer bleibt hängen, ADC- oder Timer-Flags werden nicht korrekt abgearbeitet.

- Speicherfragmentierung/Heap-Probleme: vor allem bei 32-bit-Systemen oder komplexen Stacks; unkontrollierte Pointer führen zu unvorhersehbaren Zuständen.

- EMV/ESD-Ereignisse: kurze Störungen erzeugen selten sofort Zerstörung, aber sie können Logikzustände kippen oder Codepfade „verkleben“.

- Brown-Out-Randbereiche: Spannungseinbruch ist zu kurz für einen sauberen Power-on-Reset, aber lang genug, um Zustände zu beschädigen.

Wichtig: Der Watchdog ist nicht nur „für den schlimmsten Crash“ da, sondern gerade für sporadische Teilfehler, die sonst schwer zu diagnostizieren wären.

WDT-Typen in der Praxis: Standard, Sleep-WDT und Windowed Watchdog

Je nach PIC-Familie und Projektklasse stehen unterschiedliche Watchdog-Varianten zur Verfügung. Die Begriffe unterscheiden sich leicht zwischen 8-bit-, 16-bit- und 32-bit-PICs, die Grundidee ist jedoch stabil.

Standard-WDT

Der klassische WDT läuft mit einem eigenen Takt (oft aus einem internen RC-Oszillator) und löst nach Ablauf des Timeouts einen Reset aus, wenn er nicht rechtzeitig zurückgesetzt („gefüttert“) wurde. Er eignet sich als Basisschutz für fast jedes industrielle Projekt.

WDT im Sleep-Betrieb

Viele PICs erlauben, dass der WDT auch im Sleep weiterläuft, um das System periodisch aufzuwecken oder einen Reset zu erzwingen, wenn das Aufwachen ausbleibt. Das ist nützlich für Low-Power-Steuerungen oder batteriebetriebene industrielle Sensorik.

Windowed Watchdog

Ein windowed Watchdog erhöht die Sicherheit, weil er nicht nur „zu spät“ erkennt, sondern auch „zu früh“ bestraft. Das heißt: Die Software darf den WDT nur innerhalb eines definierten Zeitfensters zurücksetzen. Ein unkontrolliertes „Dauerfüttern“ in einer schnellen Schleife (z. B. bei einem Logikfehler) wird dadurch entdeckt. In Systemen mit höheren Sicherheitsanforderungen ist ein Windowed WDT oft die bessere Wahl.

Die wichtigste Regel: Niemals den Watchdog „blind“ füttern

Ein sehr häufiger Fehler in Embedded-Projekten lautet: Der WDT wird in einer Hauptschleife oder einem Timer-Interrupt einfach regelmäßig zurückgesetzt – unabhängig davon, ob das System wirklich „gesund“ ist. Das führt dazu, dass Hänger in Subsystemen nicht erkannt werden. Die richtige Denkweise ist: Der Watchdog wird nur dann zurückgesetzt, wenn alle wesentlichen Lebenszeichen erfüllt sind.

- Gesundheitskriterien definieren: z. B. Kommunikation läuft, Sensorwerte plausibel, Hauptzustandsautomat zyklisch, keine Fehlerflags.

- Feed nur an zentraler Stelle: idealerweise in einer „Supervisor“-Funktion, die Zustände prüft.

- Keine Feed-Calls in Treibern: ein hängender Treiber darf sich nicht selbst „am Leben halten“.

- Keine Feed-Calls in endlosen Warteschleifen: Warteschleifen brauchen Timeouts, nicht Watchdog-Futter.

Timeout richtig dimensionieren: So wählen Sie eine sinnvolle WDT-Periode

Der WDT-Timeout muss groß genug sein, um normale Lastspitzen und seltene, aber legitime Abläufe zu überstehen (z. B. Flash-Schreibzyklen, Kalibrierung, Funk-Handshake). Gleichzeitig muss er klein genug sein, um Fehler schnell zu begrenzen. Eine pragmatische Startregel ist: Timeout ≈ 2–10× längste erwartete „gesunde“ Zykluszeit des kritischen Systemteils.

Wenn Ihre Hauptschleife oder Ihr Supervisor eine typische Zykluszeit

Mit einem Faktor

WDT und Echtzeit: Wenn kurze Latenz wichtiger ist als Komfort

Bei sicherheits- oder prozesskritischen Steuerungen (z. B. schnelle Aktorik, Prozessregelung) ist eine kurze Wiederherstellungszeit oft wertvoll. In solchen Fällen wählen Sie ein kürzeres Timeout und sorgen dafür, dass alle langsamen Operationen (Kommunikation, Logging, Flash-Schreiben) entweder in kleine Zeitscheiben zerlegt oder so abgesichert werden, dass sie den Supervisor nicht blockieren.

Reset-Ursache auswerten: Der WDT ist erst mit Diagnose wirklich wertvoll

Ein Watchdog-Reset ist ein Signal: „Etwas ist schiefgelaufen.“ Wenn Sie nach einem Reset nicht erfassen, warum er passiert ist, verlieren Sie eine der wichtigsten Informationsquellen aus dem Feld. Viele PICs bieten Status-Flags oder Reset-Register, mit denen sich unterscheiden lässt, ob der Reset durch WDT, Brown-Out, Power-on oder externen Reset ausgelöst wurde.

- Reset-Flags direkt beim Boot auslesen: bevor sie überschrieben werden.

- In nichtflüchtigem Speicher speichern: z. B. EEPROM/Flash oder dedizierter Log-Bereich.

- Counter führen: Anzahl WDT-Resets, letzte Ursachen, Zeitstempel (falls verfügbar).

- Service-Schnittstelle anbieten: Diagnose über UART, RS485, USB oder Debug-Pins.

Für PIC32 sind Reset-Mechanismen und Statusbits in entsprechenden Referenzabschnitten dokumentiert; ein frei zugänglicher Überblick ist beispielsweise in einer Reset-Sektion des PIC32-Referenzmaterials zu finden: PIC32 Reset-Mechanismen und Statusbits (PDF).

Die richtige Architektur: Supervisor-Pattern statt „WDT im Nebenbei“

Eine robuste industrielle PIC-Steuerung nutzt den Watchdog nicht als nachträgliches Add-on, sondern als integralen Bestandteil der Architektur. Bewährt hat sich ein Supervisor-Pattern:

- Subsysteme liefern Heartbeats: Kommunikation, Sensorik, Aktorik, UI melden „OK“ oder Fehler.

- Supervisor prüft Plausibilität: sind alle notwendigen Heartbeats frisch? Sind Fehlerflags gesetzt?

- Nur Supervisor füttert den WDT: und nur wenn alle Bedingungen erfüllt sind.

- Fail-Safe-Zustände sind klar definiert: bei Fehlern keine „halbaktiven“ Zustände.

Das Supervisor-Pattern verhindert, dass ein einzelnes Subsystem den Eindruck von Gesundheit erzeugt, obwohl das Gesamtsystem bereits blockiert ist.

Windowed WDT richtig nutzen: Schutz gegen „Runaway“-Fehler

Ein typischer Softwarefehler in Steuerungen ist ein Runaway-Zustand: Die Hauptschleife dreht sehr schnell, weil eine Wartebedingung wegfällt oder ein Timer falsch konfiguriert ist. Der Code „lebt“, aber er erfüllt seine Aufgabe nicht mehr. Ein normaler WDT erkennt das nicht, wenn er in dieser schnellen Schleife ständig zurückgesetzt wird. Ein windowed Watchdog kann genau das sichtbar machen, weil er ein Mindestzeitfenster erzwingt.

- Untergrenze: Feed zu früh → Fehler (Reset/Flag).

- Obergrenze: Feed zu spät → Fehler (Reset).

- Praktischer Nutzen: erkennt Timing-Ausreißer, Scheduler-Fehler, falsche Taktquellen, Endlosschleifen mit Feed.

Wenn Ihr PIC die Option bietet, ist windowed WDT besonders empfehlenswert für Systeme, die „zuverlässig richtig“ laufen müssen, nicht nur „irgendwie nicht hängen“.

WDT und EMV: Warum der Watchdog ein EMV-Werkzeug ist

EMV-Störungen erzeugen häufig Zustände, die nicht „sauber crashen“. Stattdessen treten sporadische Glitches auf: ein Interrupt-Flag bleibt gesetzt, ein Kommunikationszustand kippt, ein RAM-Wert wird korrumpiert. Solche Probleme lassen sich nicht allein durch Hardwaremaßnahmen eliminieren. Der Watchdog reduziert hier die Auswirkungsdauer erheblich.

- Kurze Störungen: werden durch Software-Timeouts abgefangen, ohne Reset.

- Persistente Störungen/Fehlzustände: führen zum WDT-Reset und damit zu Recovery.

- Wichtig: Ein Reset allein ist nicht genug – Ausgänge müssen nach Reset in sichere Zustände.

Das Zusammenspiel aus EMV-gerechtem Layout, Brown-Out Reset und Watchdog ist in rauen Umgebungen besonders wirksam.

Fail-Safe-Ausgänge: Damit ein WDT-Reset nicht zur Gefahr wird

Eine industrielle Steuerung darf durch einen Reset nicht in einen gefährlichen Zustand fallen. Das betrifft insbesondere Ausgänge, die Lasten schalten oder Bewegungen auslösen. Daher müssen sichere Default-Zustände bereits auf Hardware- und Boot-Ebene definiert sein.

- Pull-ups/Pull-downs: sorgen dafür, dass Ausgänge während Reset/Boot definiert sind.

- Treiber-Enable getrennt führen: Leistungstreiber erst aktivieren, wenn System „ready“.

- Relais/MOSFET-Treiber entkoppeln: keine unkontrollierten Schaltimpulse beim Reset.

- Startsequenz: erst Diagnose und Initialisierung, dann Aktoren freigeben.

Eine bewährte Praxis ist ein „SAFE“-Pin: Er bleibt per Hardware low, bis die Firmware nach erfolgreichem Self-Test explizit freigibt. Wenn der WDT resettiert, fällt SAFE automatisch zurück und die Aktorik wird deaktiviert.

Häufige Implementierungsfehler – und wie Sie sie vermeiden

- WDT zu knapp eingestellt: sporadische Resets bei Lastspitzen, scheinbar „unzuverlässige“ Steuerung.

- WDT viel zu lang: Fehler dauern unnötig lange, Anlage steht zu lange still oder verhält sich undefiniert.

- WDT blind gefüttert: echte Fehler werden nicht erkannt, nur „scheinbare Sicherheit“.

- Keine Resetdiagnose: Feldfehler bleiben Rätsel, Servicekosten steigen.

- Reset führt zu gefährlichen Ausgangszuständen: fehlende Pulls, falsche Pin-Default-Konfiguration, Treiber zu früh aktiv.

- WDT deaktiviert im Release: im Debug bequem, im Feld fatal; klare Build-Regeln nötig.

Teststrategie: Den WDT gezielt „provozieren“ statt nur hoffen

Ein Watchdog ist nur dann ein Sicherheitsgewinn, wenn Sie sein Verhalten aktiv testen. Dazu gehören Tests im Labor und in realitätsnahen Lastfällen.

- Software-Hänger simulieren: absichtliche Endlosschleife ohne Feed; prüfen, ob Reset erfolgt.

- Runaway simulieren: Feed zu schnell; bei windowed WDT muss das ebenfalls zum Reset führen.

- Kommunikationsblockade: RX-Leitung blockieren oder Busfehler erzeugen; System muss recovern.

- Versorgungsstörungen: kurze Einbrüche, Brown-Out-Fälle; Resetursachen unterscheiden.

- Fail-Safe prüfen: Ausgangszustände während Reset und nach Boot beobachten.

Ein praxisnahes Qualitätsziel ist: Nach jedem WDT-Reset soll das System innerhalb definierter Zeit in einen sicheren Grundzustand kommen und danach kontrolliert wieder in den Normalbetrieb wechseln – ohne „Halbzustände“.

WDT im Kontext von funktionaler Sicherheit: richtige Einordnung

In sicherheitsrelevanten Anwendungen wird der Watchdog häufig als ein Baustein in einem Gesamt-Sicherheitskonzept verwendet. Er ersetzt jedoch keine systematische Gefährdungsanalyse, keine redundante Abschaltung und keine normgerechte Sicherheitsarchitektur. Wenn funktionale Sicherheit relevant ist, sollten Sie sich mit den Grundprinzipien der IEC 61508 vertraut machen, die als Basisnorm für funktionale Sicherheit gilt: IEC: Überblick zur funktionalen Sicherheit (IEC 61508 Kontext). In der Praxis kann ein Watchdog Bestandteil von Diagnosemaßnahmen sein, muss aber immer im Gesamtsystem bewertet werden.

Weiterführende Ressourcen für PIC-WDT, Resetdiagnose und robuste Systeme

- Microchip Developer Help: Watchdog Timer Reset bei 8-bit PIC

- PIC32 Reset-Mechanismen und Statusbits (PDF)

- Microchip: Product Longevity (Planbarkeit in Industrieprojekten)

- Microchip AVR040: EMC Design Considerations (PDF)

- IEC: Funktionale Sicherheit im Überblick (IEC 61508 Kontext)

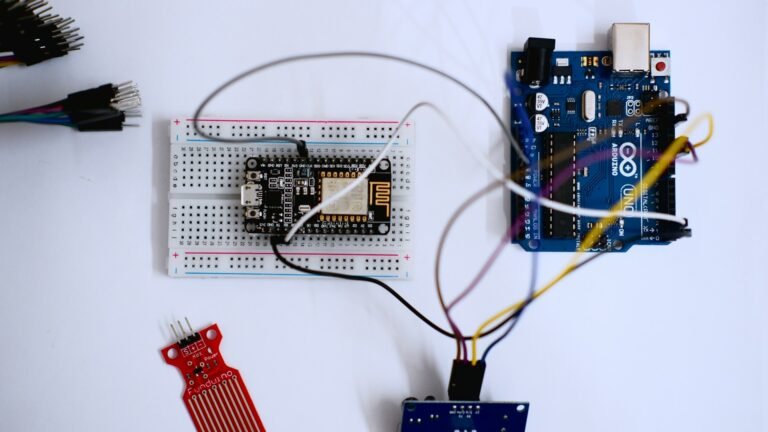

IoT-PCB-Design, Mikrocontroller-Programmierung & Firmware-Entwicklung

PCB Design • Arduino • Embedded Systems • Firmware

Ich biete professionelle Entwicklung von IoT-Hardware, einschließlich PCB-Design, Arduino- und Mikrocontroller-Programmierung sowie Firmware-Entwicklung. Die Lösungen werden zuverlässig, effizient und anwendungsorientiert umgesetzt – von der Konzeptphase bis zum funktionsfähigen Prototyp.

Diese Dienstleistung richtet sich an Unternehmen, Start-ups, Entwickler und Produktteams, die maßgeschneiderte Embedded- und IoT-Lösungen benötigen. Finden Sie mich auf Fiverr.

Leistungsumfang:

-

IoT-PCB-Design & Schaltplanerstellung

-

Leiterplattenlayout (mehrlagig, produktionstauglich)

-

Arduino- & Mikrocontroller-Programmierung (z. B. ESP32, STM32, ATmega)

-

Firmware-Entwicklung für Embedded Systems

-

Sensor- & Aktor-Integration

-

Kommunikation: Wi-Fi, Bluetooth, MQTT, I²C, SPI, UART

-

Optimierung für Leistung, Stabilität & Energieeffizienz

Lieferumfang:

-

Schaltpläne & PCB-Layouts

-

Gerber- & Produktionsdaten

-

Quellcode & Firmware

-

Dokumentation & Support zur Integration

Arbeitsweise:Strukturiert • Zuverlässig • Hardware-nah • Produktorientiert

CTA:

Planen Sie ein IoT- oder Embedded-System-Projekt?

Kontaktieren Sie mich gerne für eine technische Abstimmung oder ein unverbindliches Angebot. Finden Sie mich auf Fiverr.